《硬件架构的艺术》学习笔记(2.2)---高效门控时钟

使用或门控制在下降沿有效的时钟。(注意:使用的是高有效锁存器)

使用或门控制在下降沿有效的时钟。(注意:使用的是高有效锁存器)  对于glitch free电路当中,最后一级其实便是采用的与门控制上升沿有效的电路。只不过将锁存器换成下降沿触发的DFF。

对于glitch free电路当中,最后一级其实便是采用的与门控制上升沿有效的电路。只不过将锁存器换成下降沿触发的DFF。

发布日期:2021-05-06 19:13:41

浏览次数:14

分类:技术文章

本文共 806 字,大约阅读时间需要 2 分钟。

组合逻辑搭建的时钟产生器会引入毛刺,使功能出现问题。在同步设计中,数据输入端的毛刺不会引起任何问题,因为数据是在时钟边沿处捕获的。然而毛刺或尖峰脉冲出现在时钟输入端(或者寄存器的异步输入端)就会产生明显的影响。

内部产生的时钟

时钟信号要求全部从PLL产生。内部产生的时钟信号会出现毛刺。窄毛刺信号会违背寄存器的最小脉冲宽度要求**(寄存器对时钟信号也有要求)。**在毛刺到达时钟输入端时,如果寄存器的数据发生变化,会违背建立和保持时间。可以通过在组合逻辑后加入一级触发器加以过滤毛刺。

tco:时钟边沿到数据输出的延迟;tcomb:两级触发器间组合逻辑延迟;tskew:由于时钟生成逻辑而产生的时钟偏移量;

***此外还要注意关键一点::***由于组合逻辑而对时钟信号产生偏移量大于两级触发器的数据路径延迟时(tskew > tco + tcomb),会违背寄存器的建立时间要求。(这里通过公式:tco + tcomb < TMIN + tskew - tsetup也许会认为时序没有问题甚至是更优了,实际上会产生下图2.17的结果,外部输入信号被当前驱动的这个加上偏移量时钟所采样,那么肯定会出现建立时间违例的现象)

门控时钟方案

在传统的同步设计风格中,系统时钟连接到每个寄存器的时钟端。这使得功耗主要由三个部分组成。

- 在每个时钟沿变化的组合逻辑所产生的功耗(由于触发器驱动这些组合逻辑)。

- 由触发器产生的功耗(即使在触发器的输入和内部状态未变化,该功耗仍然存在)。

- 设计中时钟树产生的功耗(整个芯片功耗的50%消耗在时钟树)。

基于锁存器的门控时钟电路

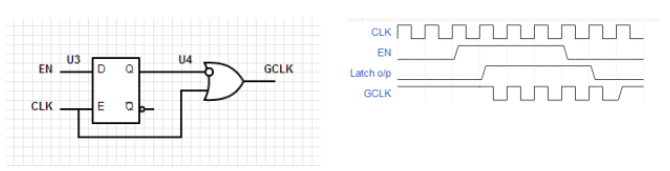

使用与门控制在上升沿有效的时钟。(注意:使用的是低有效锁存器)

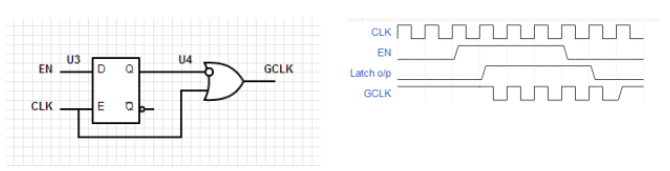

使用或门控制在下降沿有效的时钟。(注意:使用的是高有效锁存器)

使用或门控制在下降沿有效的时钟。(注意:使用的是高有效锁存器)  对于glitch free电路当中,最后一级其实便是采用的与门控制上升沿有效的电路。只不过将锁存器换成下降沿触发的DFF。

对于glitch free电路当中,最后一级其实便是采用的与门控制上升沿有效的电路。只不过将锁存器换成下降沿触发的DFF。

发表评论

最新留言

留言是一种美德,欢迎回访!

[***.207.175.100]2025年03月10日 20时46分06秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

【java】92. 反转链表 II---无需额外空间,时间复杂度O(n)!!!

2019-03-04

【java】368. 最大整除子集---使用动态规划,快速解决子问题!!!

2019-03-04

莫比乌斯函数

2019-03-04

HDU - 6514 Monitor(二维差分+二维前缀和)

2019-03-04

LINUX延时函数使用

2019-03-04

数据结构第七章(图---总结一)

2019-03-04

2020-12-24

2019-03-04

网页中常见的状态码

2019-03-04

JDBC——(5)使用Statement操作数据表的弊端

2019-03-04

JDBC——(6)PreparedStatement的使用

2019-03-04

JDBC——(6)PreparedStatement的使用——实现查询操作

2019-03-04

JDBC——小知识:PreparedStatement 和Statement的比较

2019-03-04

JDBC——(6)PreparedStatement的使用——图解查询操作流程

2019-03-04

JDBC——(6)PreparedStatement的使用——针对不同表的查询操作

2019-03-04

MyBatis——(3)MyBatis_接口式编程

2019-03-04

MyBatis——小知识:MyBatis_映射配置文件_参数值获取

2019-03-04

MyBatis——小知识:MyBatis_映射配置文件_#{}:更丰富的用法:

2019-03-04

Java后端技术体系-学习顺序总结

2019-03-04

Java多线程学习笔记

2019-03-04