《硬件架构的艺术》学习笔记(3.1)---跨时钟域设计

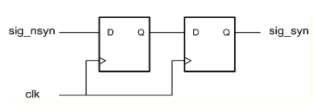

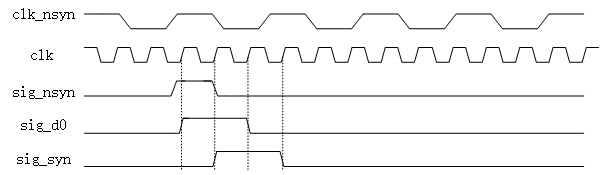

双锁存器同步法的波形图如下图。

双锁存器同步法的波形图如下图。  在上面的波形图中分析出,对于sig_nsyn信号的变化间隔有要求,最好大于{clk_nsyn + 2clk},以确保变化的信号被clk全部采样到。

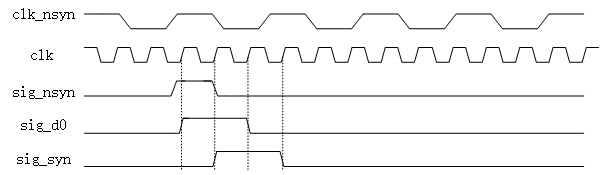

在上面的波形图中分析出,对于sig_nsyn信号的变化间隔有要求,最好大于{clk_nsyn + 2clk},以确保变化的信号被clk全部采样到。  边沿检测电路法的波形图如下图。

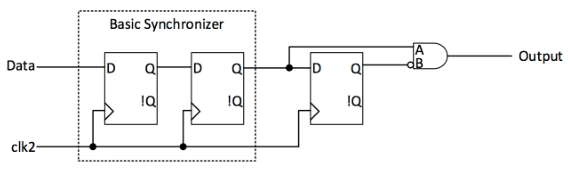

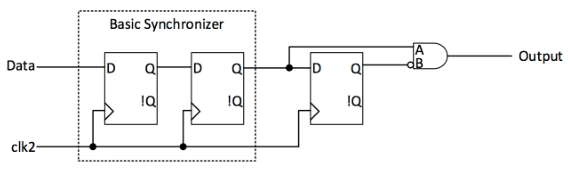

边沿检测电路法的波形图如下图。  边沿检测电路中第一级触发器用于同步信号,第二级触发器用于消除亚稳态,第三级触发器用于产生一个周期的脉冲信号。倘若在同步设计当中我们只需第三级触发器即可。当我们将A/B信号调换顺序便可以检测下降沿。

边沿检测电路中第一级触发器用于同步信号,第二级触发器用于消除亚稳态,第三级触发器用于产生一个周期的脉冲信号。倘若在同步设计当中我们只需第三级触发器即可。当我们将A/B信号调换顺序便可以检测下降沿。  单比特数据传输时,在快时钟域到慢时钟域我们应该注意数据的采样遗漏丢失问题。这时源数据应该至少保持一个目标时钟周期不变。 此外我们也可以在脉冲展宽电路后加上一级边沿检测级,用于产生一个目标时钟周期的脉冲。

单比特数据传输时,在快时钟域到慢时钟域我们应该注意数据的采样遗漏丢失问题。这时源数据应该至少保持一个目标时钟周期不变。 此外我们也可以在脉冲展宽电路后加上一级边沿检测级,用于产生一个目标时钟周期的脉冲。

发布日期:2021-05-06 19:13:42

浏览次数:11

分类:技术文章

本文共 999 字,大约阅读时间需要 3 分钟。

多时钟设计

在进行一个含有多个时钟的设计时,在仿真和综合过程中遵循一定的准则将会带来巨大的好处。

信号命名法

系统时钟:sys_clk; (system )

发送时钟:tx_clk; (transmit ) 接受时钟:rx_clk; (receive )源信号:src_sig; (sorce )

目标信号:dest_sig; (destination)跨时钟域

对于跨时钟域的信号传输问题,从信号的性质方面考虑分为两方面:1)控制信号的传输;2)数据信号的传输。从信号的宽度方面考虑又分为以下两方面:1)单bit信号传输;2)多bit信号的传输。{单比特信号一般指单比特控制信号} {多比特信号一般指多比特数据信号}

单比特(控制)信号跨时钟域传输

对于慢时钟域到快时钟域传输

1. 双锁存器同步法

双锁存器同步法的波形图如下图。

双锁存器同步法的波形图如下图。  在上面的波形图中分析出,对于sig_nsyn信号的变化间隔有要求,最好大于{clk_nsyn + 2clk},以确保变化的信号被clk全部采样到。

在上面的波形图中分析出,对于sig_nsyn信号的变化间隔有要求,最好大于{clk_nsyn + 2clk},以确保变化的信号被clk全部采样到。 2. 边沿检测电路法

边沿检测电路法的波形图如下图。

边沿检测电路法的波形图如下图。  边沿检测电路中第一级触发器用于同步信号,第二级触发器用于消除亚稳态,第三级触发器用于产生一个周期的脉冲信号。倘若在同步设计当中我们只需第三级触发器即可。当我们将A/B信号调换顺序便可以检测下降沿。

边沿检测电路中第一级触发器用于同步信号,第二级触发器用于消除亚稳态,第三级触发器用于产生一个周期的脉冲信号。倘若在同步设计当中我们只需第三级触发器即可。当我们将A/B信号调换顺序便可以检测下降沿。 边沿检测电路的注意事项:相邻的上升沿之间同步不能相隔太近,否则会采样不到边沿,造成错误。

边沿检测电路应用:对于消抖电路的实现过程中,我们可以同时采用上升沿和下降沿检测电路。对于快时钟域到慢时钟域传输

1. 脉冲展宽技术

单比特数据传输时,在快时钟域到慢时钟域我们应该注意数据的采样遗漏丢失问题。这时源数据应该至少保持一个目标时钟周期不变。 此外我们也可以在脉冲展宽电路后加上一级边沿检测级,用于产生一个目标时钟周期的脉冲。

单比特数据传输时,在快时钟域到慢时钟域我们应该注意数据的采样遗漏丢失问题。这时源数据应该至少保持一个目标时钟周期不变。 此外我们也可以在脉冲展宽电路后加上一级边沿检测级,用于产生一个目标时钟周期的脉冲。 多比特(数据)信号跨时钟域传输

一般我们说多比特信号传输时,都会默认为数据信号的传输。倘若某个模块内同时需要两条单比特控制信号,那么我们需要考虑两条单比特可能存在skew,会对结果造成影响。为了解决这个问题,我们可以先对这两条控制信号在源时钟域进行打包处理,然后再多比特信号传输或者双锁存器同步法传输。

数据信号的特点:具有连续性,需要较快的传输速度。采用上述同步法都会出现传输数据不连贯的问题,这里会采用FIFO或者加入握手信号。

发表评论

最新留言

能坚持,总会有不一样的收获!

[***.219.124.196]2025年03月30日 11时20分06秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

2021年T电梯修理考试技巧及T电梯修理模拟考试软件

2019-03-03

2021年R2移动式压力容器充装考试题及R2移动式压力容器充装找答案

2019-03-03

2021年电工(初级)考试及电工(初级)证考试

2019-03-03

2021年安全员-B证(山东省)考试APP及安全员-B证(山东省)考试技巧

2019-03-03

2021年安全员-A证(山东省)考试题及安全员-A证(山东省)报名考试

2019-03-03

2021年G1工业锅炉司炉考试报名及G1工业锅炉司炉模拟考试题库

2019-03-03

大数据学习之Spark——00Spark项目的pom.xml文件

2019-03-03

大数据学习之Spark——01Spark概述

2019-03-03

比特币史话·78 | 有容乃大(2): 零食售卖机

2019-03-03

比特币史话·96 | 隐私(3): 熔币重铸

2019-03-03

Fire prejudice: 巴菲特搭档芒格首度认可比特币

2019-03-03

GLUT和wxWidgets在OpenGL开发中的比较

2019-03-03

CodeBlocks开发wxWidgets环境配置详细

2019-03-03

Qt 转向 LGPL之后,wxWidgets 路在何方

2019-03-03

[翻译]2009年6月wxWidgets更新 - 支持图标的wxButton

2019-03-03

wxSqlite3 和 wxPropertyGrid 类库的说明

2019-03-03

天涯人脉通讯录 - 设计草图

2019-03-03