74160ENT引脚设计法接成100进制加法计数器

发布日期:2021-05-08 01:15:00

浏览次数:24

分类:精选文章

本文共 623 字,大约阅读时间需要 2 分钟。

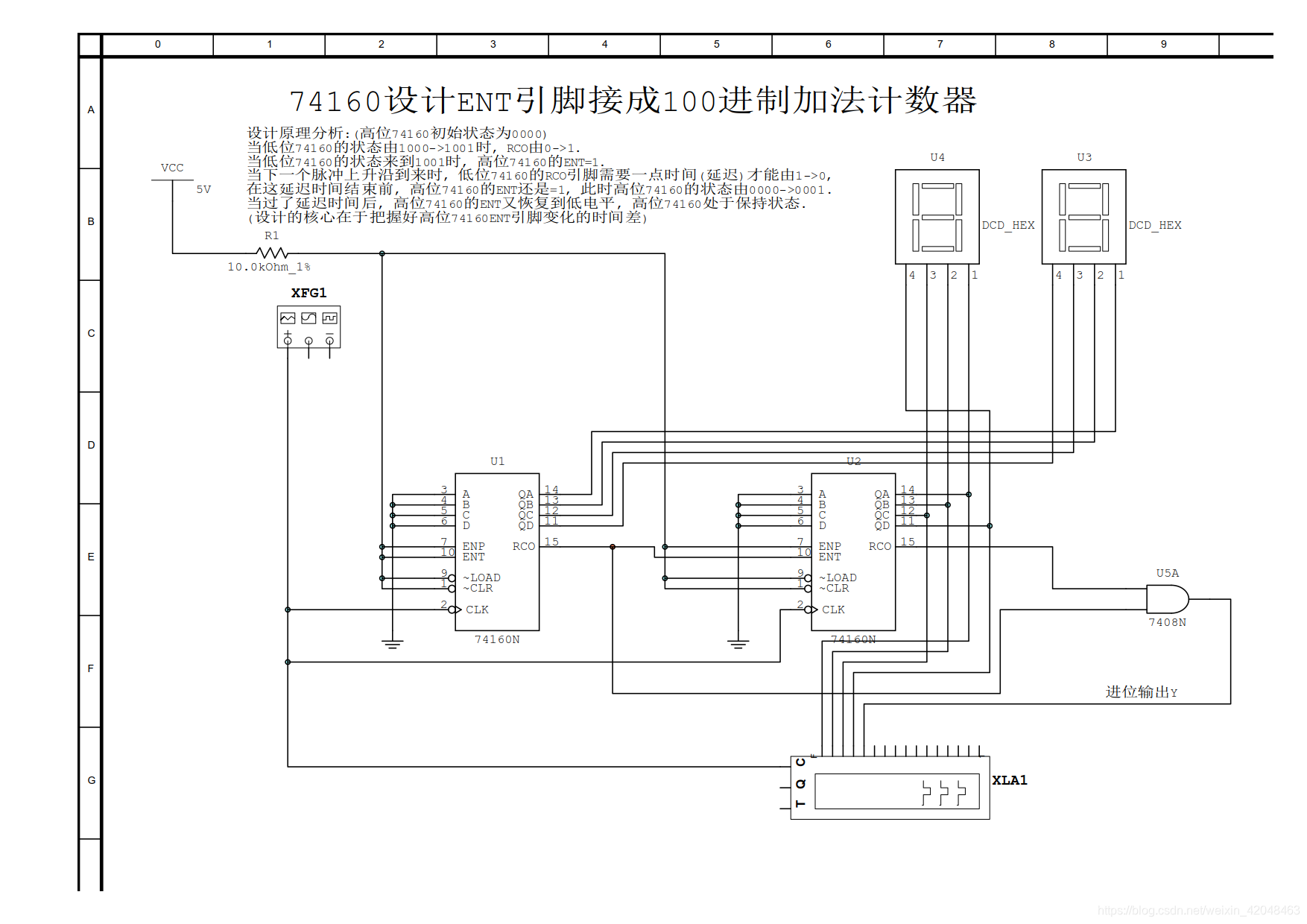

之前和大家分享了同步置数法和异步清零法, 这里再和大家介绍另一种方法——ENT引脚设计法.

在开始设计前, 我们要明确ENT引脚和ENP引脚的作用: 当ENT=ENP=1时, 74160开始计数; 当ENT=0或ENP=0时, 74160处于保持状态. 这里我以ENT引脚(选择ENP引脚也可以)作为设计对象, 准备接成100进制加法计数器.

题目: 用2片74160、 1片与门接成100进制加法计数器.

分析(从下述电路图入手):

要接成100进制加法计数器, 重点在于处理低位74160从1001->0000时向高位74160提供进位信号的问题.

当低位74160到达状态1001后, 其RCO引脚变为高电平; 此时高位74160的ENT引脚也随之变为高电平. 当下一系统上升沿信号到来时, 两片74160的状态都+1, 而后低位74160的状态变为0000, 其RCO引脚随之变为低电平, 高位74160的ENT引脚也随之变为低电平. 当系统上升沿信号再次到来时, 低位74160依旧实现+1操作, 而高位74160由于其ENT引脚变为低电平, 则处于保持状态: 直到低位74160的状态再次到达1001时, 再次重复上述过程 .

如此设计的100进制加法计数电路, (比如)在09跳变为10时, 具有良好的视觉统一性: 而采用进位级联方式构成的100进制加法计数电路就不具备良好的视觉统一性(09跳变为10时, 低位先变, 高位后变).

发表评论

最新留言

感谢大佬

[***.8.128.20]2025年04月05日 11时00分30秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

weblogic之cve-2015-4852

2021-05-08

Java注释

2021-05-08

C++ 函数重载

2021-05-08

使用mybatis-generator生成底层

2021-05-08

Mybatis【5】-- Mybatis多种增删改查那些你会了么?

2021-05-08

计算输入的一句英文语句中单词数

2021-05-08

lvs+keepalive构建高可用集群

2021-05-08

6 个 Linux 运维典型问题

2021-05-08

取消vim打开文件全是黄色方法

2021-05-08

一个系统部署多个tomcat实例

2021-05-08

HP服务器设置iLO

2021-05-08

从头实现一个WPF条形图

2021-05-08

使用QT实现一个简单的登陆对话框(纯代码实现C++)

2021-05-08

QT :warning LNK4042: 对象被多次指定;已忽略多余的指定

2021-05-08

GLFW 源码 下载-编译-使用/GLAD配置

2021-05-08

针对单个网站的渗透思路

2021-05-08

Typescript 学习笔记六:接口

2021-05-08

02、MySQL—数据库基本操作

2021-05-08

OpenJDK1.8.0 源码解析————HashMap的实现(一)

2021-05-08