linux基础梳理2019.01.22(makefile)

发布日期:2021-05-06 23:06:50

浏览次数:22

分类:精选文章

本文共 891 字,大约阅读时间需要 2 分钟。

makefile

makefile的三要素:

- 目标

- 依赖——可以不写

- 规则命令——可以不写

写法:

目标:依赖

tab键规则命令

例子:

利用main.c文件调用其余文件中的函数。

![]()

实现样例:

![]()

makefile的弊端:

如果更改其中一个文件,所有的源码都要重新编译。

解决方案:

编译过程分解。先生成 .o 文件,使用 .o 文件来得到成果。

要想分解编译过程,先来分析一下编译的原理:

编译的“规则是递推的”,比如下图中的可执行文件 app, 他依赖main.o , add.o 和 div.o 生成。编译时,如果没有main.o 文件,则编译器回去寻找有没有main.o的生成规则。这就是“规则是递推的”。

根据规则,我们把上面的makefile重新写一下:

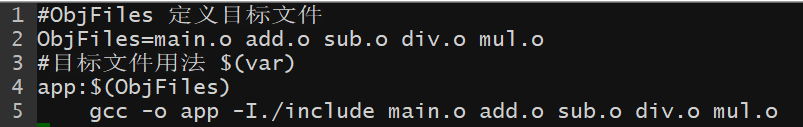

makefile中的定义变量

可以定义变量 ObjFiles=main.o add.o sub.o div.o …

变量的使用:$(ObjFiles),$(变量名)

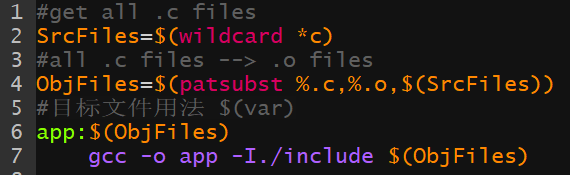

函数

- wildcard——可以进行文件匹配

- patsubst——内容的替换

wildcard使用例子:

makefile的隐含规则——默认处理第一个目标,我们需要他处理我们的test目标,测试一下函数的功能,因此可以这样:

make test

patsubst的使用例子

makefile的变量

- $@ 代表目标

- $^ 代表全部依赖

- $< 第一个依赖

- $? 第一个变化的依赖

因此上面的第一版makefile可以改成

其中,%表示通配。$@, $<这样的变量,只能在规则中出现。

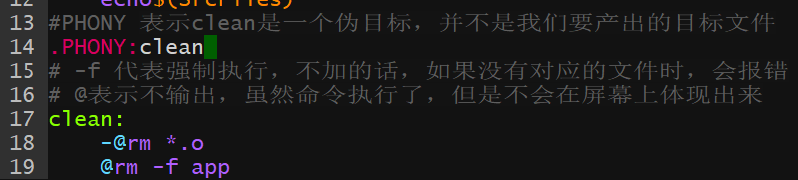

makefile清理

- -f 代表强制执行,不加的话,如果没有对应的文件时,会报错

- @表示不输出,虽然命令执行了,但是不会在屏幕上体现出来

- - 表示,即使这个命令报错了,也会执行(和 -f的功效类似)

上面的代码存在一个问题——clean的作用是清理,执行clean之后,会产出一个目标文件“clean”。该如何解决这个问题?

使用——.PHONY,定义伪目标,防止歧义

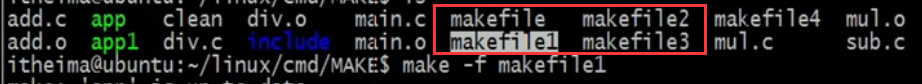

多个makefile文件时,如何指定执行哪一个?

执行以下命令即可:

make -f makefile1

发表评论

最新留言

路过,博主的博客真漂亮。。

[***.116.15.85]2025年04月09日 00时05分18秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

sharding-jdbc 分库分表的 4种分片策略,还蛮简单的

2021-05-09

分库分表的 9种分布式主键ID 生成方案,挺全乎的

2021-05-09

MySQL不会丢失数据的秘密,就藏在它的 7种日志里

2021-05-09

Python开发之序列化与反序列化:pickle、json模块使用详解

2021-05-09

回顾-生成 vs 判别模型-和图

2021-05-09

采坑 - 字符串的 "" 与 pd.isnull()

2021-05-09

无序列表 - 链表

2021-05-09

SQL 查询强化 - 数据准备

2021-05-09

SQL 强化练习 (四)

2021-05-09

SQL 强化练习 (八)

2021-05-09

Excel 拼接为 SQL 并打包 exe

2021-05-09

Pandas数据分析从放弃到入门

2021-05-09

Matplotlib绘制漫威英雄战力图,带你飞起来!

2021-05-09

机器学习是什么

2021-05-09

《小王子》里一些后知后觉的道理

2021-05-09

《自私的基因》总结

2021-05-09

《山海经》总结

2021-05-09

《非暴力沟通》总结

2021-05-09

《你当像鸟飞往你的山》总结

2021-05-09

《我是猫》总结

2021-05-09