《硬件架构的艺术》学习笔记(4)---时钟分频设计

以计数器的方式来实现。当cnt = 0 和 cnt = 2 的(在cnt = 1 和 cnt = 3 )时候将输出取反。需要两个always块便可以描述。

以计数器的方式来实现。当cnt = 0 和 cnt = 2 的(在cnt = 1 和 cnt = 3 )时候将输出取反。需要两个always块便可以描述。  在《硬件架构的艺术》中,作者采用的TFF的方式进行三分频设计。T触发器的状态转移:Q* = T~Q + ~TQ,时序图见上图左图。首先在cnt = 0、cnt = 2的时候产生T触发器使能信号en1、en2,然后分别对TFF1、TFF2上升沿、下降沿触发得到tff1、tff2的时序图,最后将tff1 与 tff2信号异或处理便得到最终三分频输出。

在《硬件架构的艺术》中,作者采用的TFF的方式进行三分频设计。T触发器的状态转移:Q* = T~Q + ~TQ,时序图见上图左图。首先在cnt = 0、cnt = 2的时候产生T触发器使能信号en1、en2,然后分别对TFF1、TFF2上升沿、下降沿触发得到tff1、tff2的时序图,最后将tff1 与 tff2信号异或处理便得到最终三分频输出。  通过寄存器Q1来产生0-0-1的序列。通过上述卡诺图得知:D0 = ~Q1 & ~Q0。得到的电路图及时序图如下。

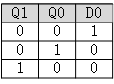

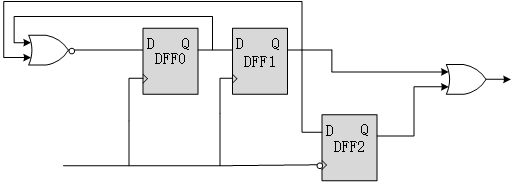

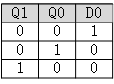

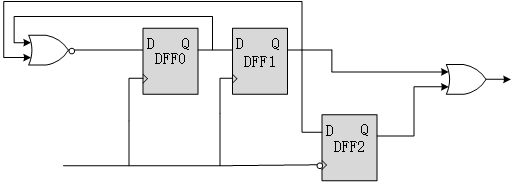

通过寄存器Q1来产生0-0-1的序列。通过上述卡诺图得知:D0 = ~Q1 & ~Q0。得到的电路图及时序图如下。

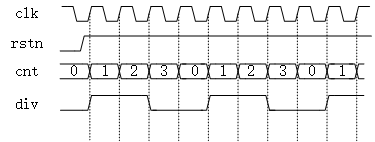

首先需要5bit的移位寄存器,初始值为00001;然后将dff2信号下降沿触发形成1/2clk;最后再将dff0与dff2-180或运算,不会出现毛刺。对于其余的小数分频如3.5、4.5、5.5我们也要注意最后信号的毛刺问题。

首先需要5bit的移位寄存器,初始值为00001;然后将dff2信号下降沿触发形成1/2clk;最后再将dff0与dff2-180或运算,不会出现毛刺。对于其余的小数分频如3.5、4.5、5.5我们也要注意最后信号的毛刺问题。

发布日期:2021-05-06 19:13:43

浏览次数:21

分类:技术文章

本文共 1621 字,大约阅读时间需要 5 分钟。

时钟分频设计

主要分享两部分:1)整数分频、2)小数分频。

1. 整数分频

整数分频又分为:1.1)偶数分频、1.2)奇数分频 {50%占空比}

1.1偶数分频

以4分频电路为例。

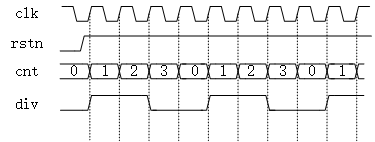

以计数器的方式来实现。当cnt = 0 和 cnt = 2 的(在cnt = 1 和 cnt = 3 )时候将输出取反。需要两个always块便可以描述。

以计数器的方式来实现。当cnt = 0 和 cnt = 2 的(在cnt = 1 和 cnt = 3 )时候将输出取反。需要两个always块便可以描述。 **verilog实现技巧:下述代码当中,采用<counter[0] == 1>**的方式作为条件于省略掉的代码相比较可以减少硬件资源。

module div_four( input wire clk, input wire rstn, input wire en, output wire div_4);reg [1:0] counter;always @ (posedge clk or negedge rstn) begin if(rstn == 0) counter <= 0; else if(en == 1) counter <= counter + 1; else counter <= 0;endreg div_four;always @ (posedge clk or negedge rstn) begin if(rstn == 0) div_four <= 0;/* else if(counter == 'd1) div_four <= 1; else if(&counter == 1) div_four <= 0; */ else if(counter[0] == 1) div_four <= !div_four;endassign div_4 = div_four;endmodule

1.2奇数分频

对于占空比非50%的奇数分频,通过计数器便可以实现。那么对于占空比50%的奇数分频这里介绍两种实现方式:1)计数器方式、2)序列发生器方式。以三分频为例。

1. 计数器方式

在《硬件架构的艺术》中,作者采用的TFF的方式进行三分频设计。T触发器的状态转移:Q* = T~Q + ~TQ,时序图见上图左图。首先在cnt = 0、cnt = 2的时候产生T触发器使能信号en1、en2,然后分别对TFF1、TFF2上升沿、下降沿触发得到tff1、tff2的时序图,最后将tff1 与 tff2信号异或处理便得到最终三分频输出。

在《硬件架构的艺术》中,作者采用的TFF的方式进行三分频设计。T触发器的状态转移:Q* = T~Q + ~TQ,时序图见上图左图。首先在cnt = 0、cnt = 2的时候产生T触发器使能信号en1、en2,然后分别对TFF1、TFF2上升沿、下降沿触发得到tff1、tff2的时序图,最后将tff1 与 tff2信号异或处理便得到最终三分频输出。 后来想了一下,完全可以用DFF的方式来实现。时序图见上图右图。需要四个always块便可以描述。D触发器的状态转移:Q* = D,在cnt = 1的时候上升沿触发dff1翻转,在cnt = 0的时候下降沿触发dff2翻转,然后将dff1 与 dff2信号异或处理。

2. 序列发生器方式

若以序列发生器的形式来进行三分频设计,我们需要产生0-0-1的这样的序列。列举卡诺图: 通过寄存器Q1来产生0-0-1的序列。通过上述卡诺图得知:D0 = ~Q1 & ~Q0。得到的电路图及时序图如下。

通过寄存器Q1来产生0-0-1的序列。通过上述卡诺图得知:D0 = ~Q1 & ~Q0。得到的电路图及时序图如下。

3. 两种方式对比

- 这两种方式都需要下降沿触发的触发器才可以产生占空比50%的奇数分频。

- 第一种方案需要4个DFF;第二种方案需要3个DFF。

- 这两种方案都**不会产生毛刺(后续组合运算时,只有一端变化),**不存在竞争冒险现象。

- 个人偏好第二种序列发生器,第一种没有那么好想象的到。

2. 小数分频

首先明确一点:小数分频一定不会出现50%占空比的情况,除非出现时钟skew。

以2.5倍分频计数器为例: 首先需要5bit的移位寄存器,初始值为00001;然后将dff2信号下降沿触发形成1/2clk;最后再将dff0与dff2-180或运算,不会出现毛刺。对于其余的小数分频如3.5、4.5、5.5我们也要注意最后信号的毛刺问题。

首先需要5bit的移位寄存器,初始值为00001;然后将dff2信号下降沿触发形成1/2clk;最后再将dff0与dff2-180或运算,不会出现毛刺。对于其余的小数分频如3.5、4.5、5.5我们也要注意最后信号的毛刺问题。 发表评论

最新留言

逛到本站,mark一下

[***.202.152.39]2025年03月18日 18时26分39秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

Node.js response 页面中文乱码

2019-03-04

谷歌浏览器 禁用JavaScript

2019-03-04

gitee 修改个人域名 个人空间地址 URL

2019-03-04

C++11中bind的使用错误

2019-03-04

Android中CMake的使用之一初步总结

2019-03-04

一起学智能合约之四表达式和控制结构

2019-03-04

futex同步机制分析之三内核实现

2019-03-04

多线程的伪共享

2019-03-04

flink分析使用之五工作图的生成和分发

2019-03-04

基于OpenCV的路面质量检测

2019-03-04

Spring Cloud系列_11 Feign负载均衡、请求传参

2019-03-04

leetcode 543. Diameter of Binary Tree

2019-03-04

VSLAM系列原创01讲 | 深入理解ORB关键点提取:原理+代码

2019-03-04

卡尔曼滤波器的特殊案例

2019-03-04

基于Opencv的图像单应性转换实战

2019-03-04

【C++简明教程】Python和C++指定元素排序比较

2019-03-04

视觉实战|使用人工神经网络进行图像分类

2019-03-04

3D感知技术及实践

2019-03-04

北大读博手记:怎样完成自己的博士生涯?非常具有指导性!

2019-03-04

世界上有哪些代码量很少,但很牛逼很经典的算法或项目案例?

2019-03-04