本文共 1179 字,大约阅读时间需要 3 分钟。

参考链接:

利用FPGA Editor将RO制作成Hard Macro的具体步骤如下:

1)完成RO代码的编写之后,在ucf文件中对RO的布局位置进行约束,完成综合及布局布线之后,打开FPGA Editor工具查看实际的电路版图。

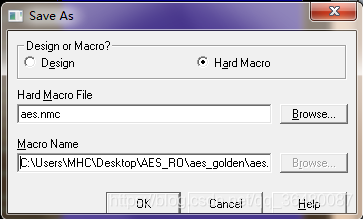

2)将文件另存为硬核文件,这样将在工程下生成一个nmc文件。

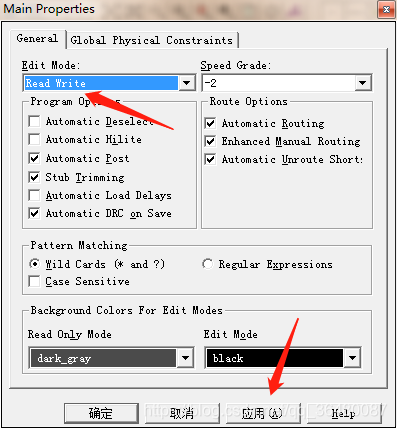

3)更改文件属性,点击File菜单下的Main Properties选项卡,将Edit Mode更改为可读写。

4)分别选取输入输出端口,点击Tools菜单下的Place > Unplace选项,以删除输入输出端口。

5)删除输入输出端口后,相关Slice上将出现绿色标记,这个标记就是之前删除的输入输出路径。分别选取输入输出端口,点击Edit菜单下的Add Hard Macro External Pin选项,添加硬核的输入输出端口,特别注意:这里的端口名必须要和实例化的端口名一致。

6)选取其中一个Slice,点击Edit菜单下的Set Marco Reference Comp选项,建立一个参考点,以约束实例化硬核时的布局位置。

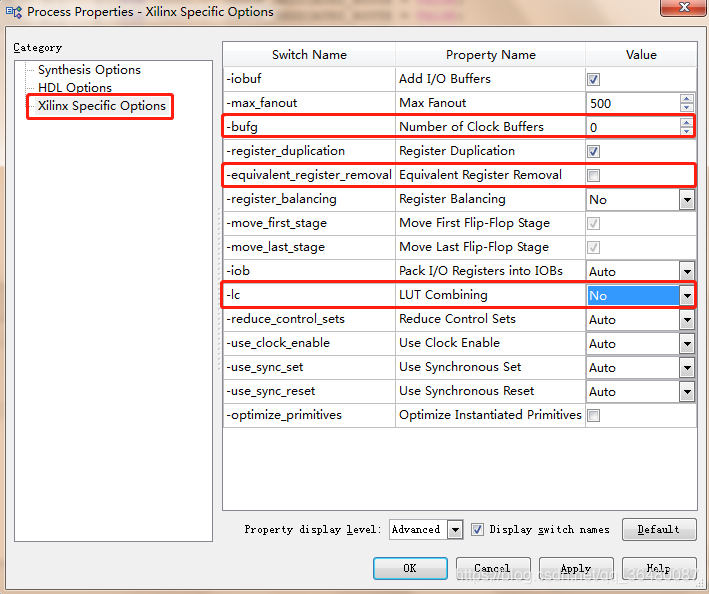

由于制作硬核的过程中不能有全局电源信号,这里主要表现为global logic 1,因此需要修改设计的综合属性,使产生的global logic 1尽量少。主要修改了以下几项:

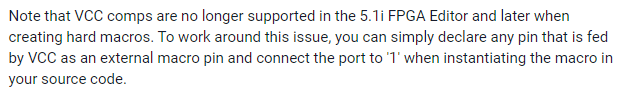

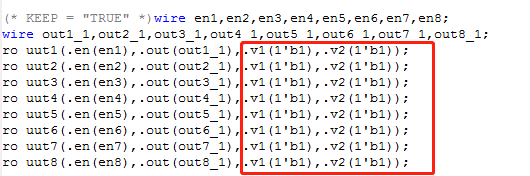

在修改综合属性之后,global logic 1的数量虽然有所减少,但依然存在,这时候的解决方法是:将连接global logic 1的net删除,然后将对应的端口添加成硬核的输入端口(External Pin),在顶层模块调用硬核时直接将给该端口赋值高电平1。

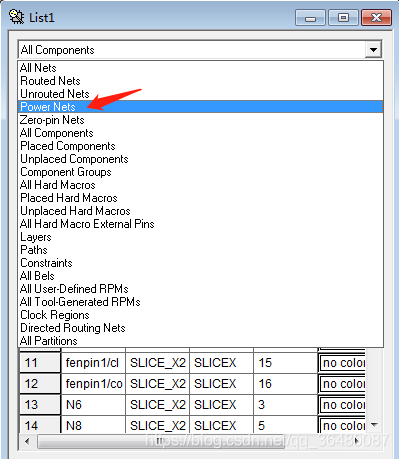

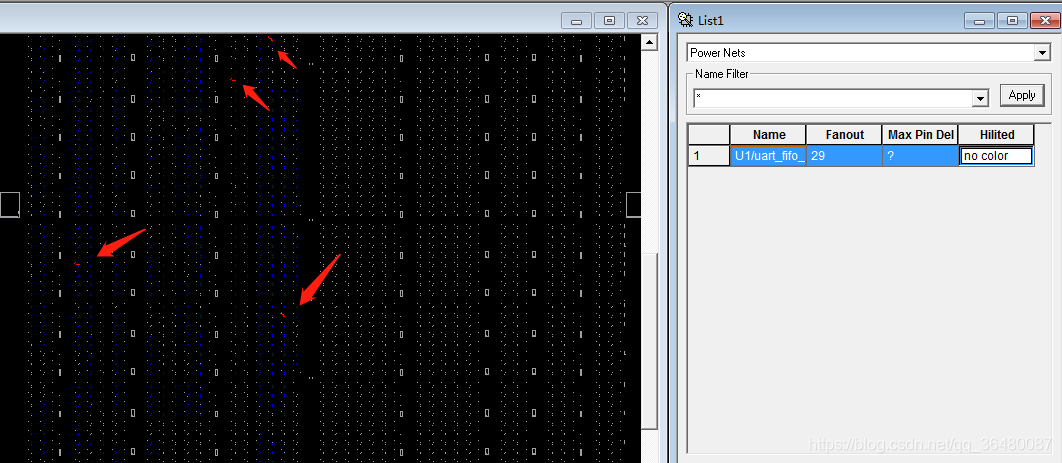

1. 找出设计中存在的global logic 1;

2. 更改文件属性为“Read Write”,选中连接到global logic 1的net,右键删除;

3. 将文件保存为nmc格式;

4. 将连接到global logic 1的端口添加为硬核的输入端口(External Pin);

5.添加其他的输入Pin,最后设定参考部分(reference comp),完成硬核制作;

6.在顶层模块中实例化时将原来设计中连接到global logic 1的输入端口直接赋值为高电平1。

将AES电路制作成硬核时,因为多个输入端如clk_15Mhz、rst_n等都连接到了电路中的多个模块,属于多扇出信号,因此将其添加为硬核的输入端口时,需要让其先经过一个buffer,然后再将这个buffer的输入端添加为硬核的输入pin。

首先尝试了让信号经过BUFG结构,但因为BUFG是全局缓冲,因此只有在FPGA 芯片的固定位置才有BUFG,所以之后调用AES硬核,改变其布局位置时可能会遇到问题,因此方案变为使用普通的buffer类型如IBUF,或者直接用两级反相器起到buffer的作用。

转载地址:https://blog.csdn.net/qq_36480087/article/details/108513397 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关于作者