LCD1602液晶屏的FPGA驱动(1)————读,写模块

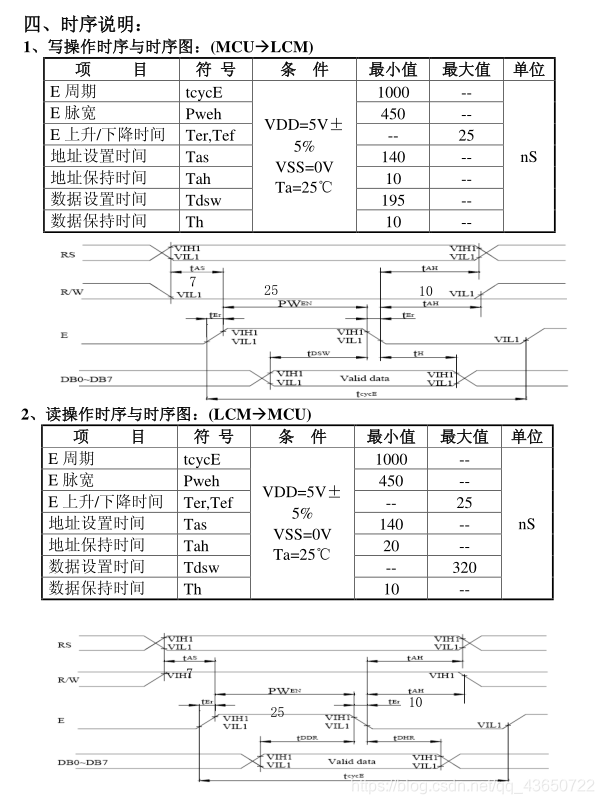

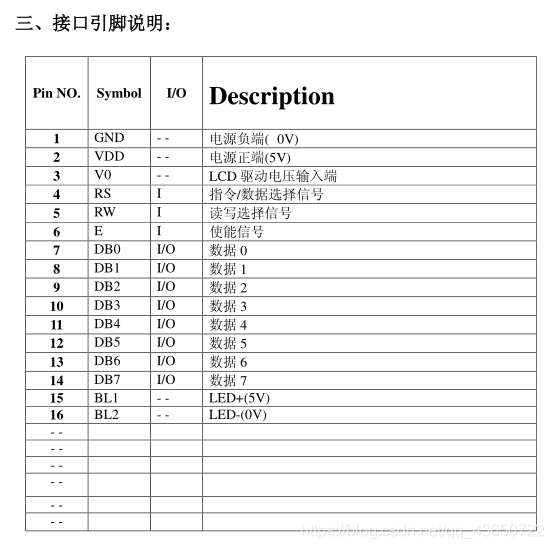

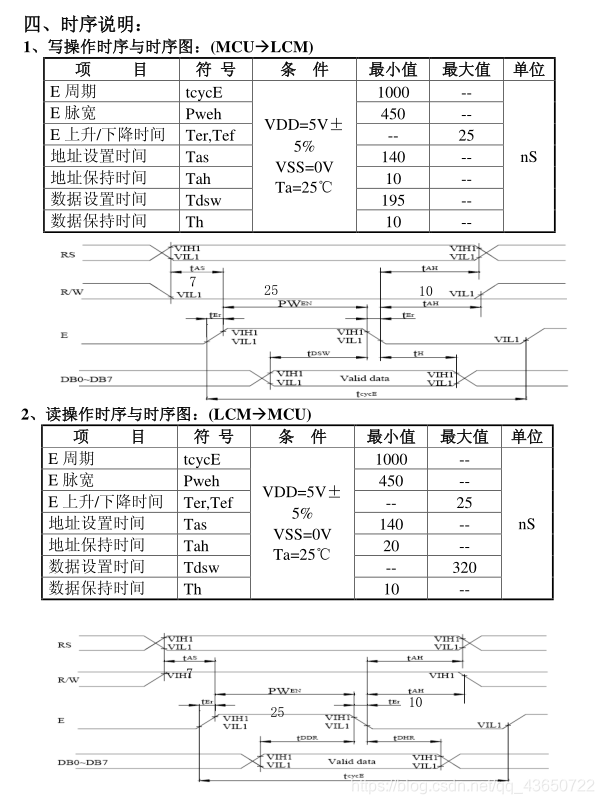

LCD1602的读写时序很容易,只需在对应的时刻对RS,RW,E操作即可,DB数据总线保持对应的时间或在对应时间读取。

LCD1602的读写时序很容易,只需在对应的时刻对RS,RW,E操作即可,DB数据总线保持对应的时间或在对应时间读取。

发布日期:2021-05-07 22:56:18

浏览次数:19

分类:精选文章

本文共 4376 字,大约阅读时间需要 14 分钟。

说明书摘要

LCD1602的读写时序很容易,只需在对应的时刻对RS,RW,E操作即可,DB数据总线保持对应的时间或在对应时间读取。

LCD1602的读写时序很容易,只需在对应的时刻对RS,RW,E操作即可,DB数据总线保持对应的时间或在对应时间读取。 Verilog代码

LCD写模块

//Name:Lcd_read_mod//Author:Yang_Cheng_Yu//Date:2020/4/18//==================defines=====================`define SIM/**/module lcd_write( //================System Signal================ input clk, input rst_n, //================Interface==================== input rs_in, output reg RS,//指令数据选择 output reg RW, output reg E, output reg[7:0] DB, input wr_req, input[7:0] data); //================parameters=================== `ifndef SIM `else `endif //================System regs================== reg wr_req_t0; reg wr_req_t1; wire trig_wr_req; reg flag_wr; reg flag_wr_end; reg[9:0] cnt; //================Main Codes=================== //wr_req always @(posedge clk)begin wr_req_t0 <= wr_req; wr_req_t1 <= wr_req_t0; end assign trig_wr_req = wr_req_t0&(~wr_req_t1); // output reg RS,//指令数据选择 always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) RS <= 1'b1; else if(flag_wr==1'b0&&trig_wr_req==1'b1) RS <= rs_in; else if(cnt==7+25+10) RS <= 1'b1; end //output reg RW, always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) RW <= 1'b1; else if(flag_wr==1'b0&&trig_wr_req==1'b1) RW <= 1'b0; else if(cnt==7+25+10) RW <= 1'b1; end //E always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) E <= 1'b0; else if(cnt==7) E <= 1'b1; else if(cnt==7+25) E <= 1'b0; end //DB always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) DB <= 'd0; else if(flag_wr==1'b1&&cnt==7) DB <= data; else if(cnt==7+25+10) DB <= 'd0; end //flag_wr always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) flag_wr <= 1'b0; else if(flag_wr==1'b0&&trig_wr_req==1'b1) flag_wr <= 1'b1; else if(cnt==7+25+10) flag_wr <= 1'b0; end //flag_wr_end always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) flag_wr_end <= 1'b0; else if(cnt==7+25+10) flag_wr_end <= 1'b1; else flag_wr_end <= 1'b0; end //cnt always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) cnt <= 'd0; else if(flag_wr==1'b1&&cnt==7+25+10) cnt <= 'd0; else if(flag_wr==1'b1) cnt <= cnt + 1'b1; else cnt <= 'd0; end endmodule

LCD读模块

//Name:Lcd_read_mod//Author:Yang_Cheng_Yu//Date:2020/4/18//==================defines=====================`define SIM/**/module lcd_read( //================System Signal================ input clk, input rst_n, //================Interface==================== output reg RS,//指令数据选择 output reg RW, output reg E, input [7:0] DB, output reg[7:0] data_rd, output reg flag_rd_end, input rd_req, input rs_in); //================parameters=================== `ifndef SIM `else `endif //================System regs================== reg flag_rd; reg rd_req_t0; reg rd_req_t1; wire trig_rd_req; reg[15:0] cnt; //================Main Codes=================== //rd_req always @(posedge clk)begin rd_req_t0 <= rd_req; rd_req_t1 <= rd_req_t0; end assign trig_rd_req = rd_req_t0&(~rd_req_t1); //RS always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) RS <= 1'b1; else if(flag_rd==1'b0&&trig_rd_req==1'b1) RS <= rs_in; else if(flag_rd==1'b1&&cnt==7+25+10) RS <= 1'b1; end //flag_rd always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) flag_rd <= 1'b0; else if(flag_rd==1'b0&&trig_rd_req==1'b1) flag_rd <= 1'b1; else if(flag_rd==1'b1&&cnt==7+25+10) flag_rd <= 1'b0; end //RW always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) RW <= 1'b0; else if(flag_rd==1'b0&&trig_rd_req==1'b1) RW <= 1'b1; else if(flag_rd==1'b1&&cnt==7+25+10) RW <= 1'b0; end //data_rd always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) data_rd <= 'd0; else if(flag_rd==1'b1&&cnt==7+14) data_rd <= DB; end //flag_rd_end always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) flag_rd_end <= 1'b0; else if(flag_rd==1'b1&&cnt==7+25+10) flag_rd_end <= 1'b1; else flag_rd_end <= 1'b0; end //cnt always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) cnt <= 'd0; else if(flag_rd==1'b1) if(cnt==7+25+10) cnt <= 'd0; else cnt <= cnt + 1'b1; else cnt <= 'd0; end //E always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0) E <= 1'b0; else if(flag_rd==1'b1&&cnt==7) E <= 1'b1; else if(flag_rd==1'b1&&cnt==7+25) E <= 1'b0; end endmodule

发表评论

最新留言

留言是一种美德,欢迎回访!

[***.207.175.100]2025年03月25日 04时53分17秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

2021-4-28【PTA】【L2-1 包装机 (25 分)】

2021-05-07

Arduino mega2560+MPU6050利用加速度值控制舵机

2021-05-07

紫书——蛇形填数

2021-05-07

A Guide to Node.js Logging

2021-05-07

webwxbatchgetcontact一个神奇的接口

2021-05-07

Edge浏览器:你的的内核我的芯

2021-05-07

【考研英语-基础-简单句】简单句的核心变化_谓语情态

2021-05-07

Jetson AGX Xavier硬件自启动

2021-05-07

统计字符数

2021-05-07

JS数据类型的判断

2021-05-07

实现一个简易Vue(三)Compiler

2021-05-07

仿小米商城(上)

2021-05-07

自动安装服务2

2021-05-07

js的各种数据类型判断(in、hasOwnProperty)

2021-05-07

严格模式、混杂模式与怪异模式

2021-05-07

HTML 和 CSS 简单实现注册页面

2021-05-07

(SpringMVC)springMVC.xml 和 web.xml

2021-05-07

(LeetCode)Java 求解搜索旋转排序数组

2021-05-07