STM32H750的FMC时钟问题

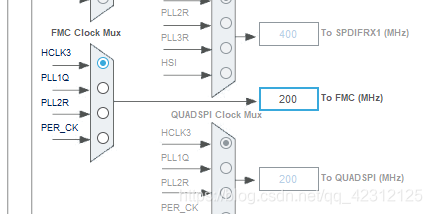

这是我的时钟相关配置,理论上是没问题,也没有达到最高频率480MHz。 从野火的FMC的时钟配置来看,

这是我的时钟相关配置,理论上是没问题,也没有达到最高频率480MHz。 从野火的FMC的时钟配置来看,  没错就是这里,本来在程序上应该配置的是PLL2R这个地方的时钟,用这个地方的时钟输出到FMC上,但是却是默认选择HCLK3,所以,这就是导致为什么PLL2初始化一直失败的原因!这时候将它选中PLL2Q,

没错就是这里,本来在程序上应该配置的是PLL2R这个地方的时钟,用这个地方的时钟输出到FMC上,但是却是默认选择HCLK3,所以,这就是导致为什么PLL2初始化一直失败的原因!这时候将它选中PLL2Q,  将会和预期的一样,得到360MHz的时钟。通过STM32CubeMX生成工程,后添加相关驱动文件,发现SDRAM的初始化不会再卡住了。这时候,我们比对两个工程的SystemClock_Config(),就很容易发现多了一句话,

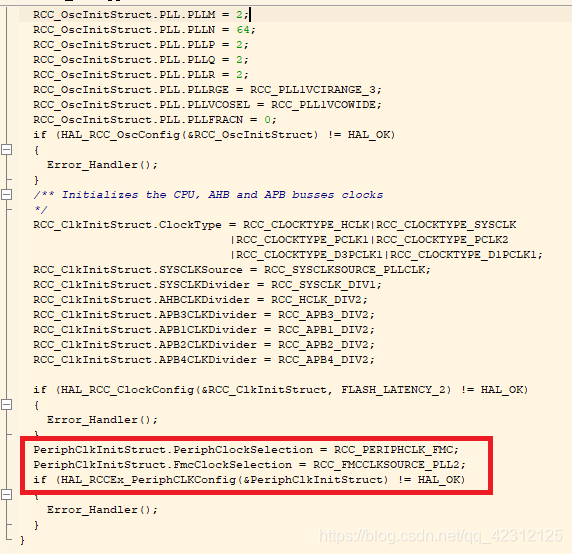

将会和预期的一样,得到360MHz的时钟。通过STM32CubeMX生成工程,后添加相关驱动文件,发现SDRAM的初始化不会再卡住了。这时候,我们比对两个工程的SystemClock_Config(),就很容易发现多了一句话,  没错,就是因为这里的选择问题,FMC的时钟源,必须选择RCC_FMCCLKSOURCE_PLL2的时候,才能对PLL2的配置生效,否则配置将ERROR。这问题搞了我一晚上,真不应该啊!

没错,就是因为这里的选择问题,FMC的时钟源,必须选择RCC_FMCCLKSOURCE_PLL2的时候,才能对PLL2的配置生效,否则配置将ERROR。这问题搞了我一晚上,真不应该啊!

发布日期:2021-05-07 22:29:18

浏览次数:23

分类:精选文章

本文共 1191 字,大约阅读时间需要 3 分钟。

问题:配置STM32H750的FMC时钟时,会配置失败?

这个问题我是怎么发现的呢?首先我一般的风格不会使用while(1)这种等待的,一般会选择加入超时机制来保证系统的正常运行。但是在我移植野火的STM32H750的SDRAM的程序的时候,我发现程序停留在SDRAM_Init()里面的while(1)中。

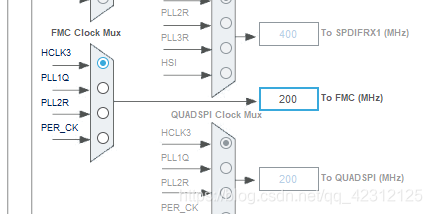

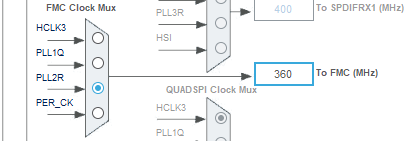

关于这个问题,先看STM32H750的时钟树: 这是我的时钟相关配置,理论上是没问题,也没有达到最高频率480MHz。 从野火的FMC的时钟配置来看,

这是我的时钟相关配置,理论上是没问题,也没有达到最高频率480MHz。 从野火的FMC的时钟配置来看, RCC_PeriphClkInit.PeriphClockSelection = RCC_PERIPHCLK_FMC; RCC_PeriphClkInit.PLL2.PLL2M = 5; RCC_PeriphClkInit.PLL2.PLL2N = 144; RCC_PeriphClkInit.PLL2.PLL2P = 2; RCC_PeriphClkInit.PLL2.PLL2Q = 2; RCC_PeriphClkInit.PLL2.PLL2R = 3; RCC_PeriphClkInit.PLL2.PLL2RGE = RCC_PLL2VCIRANGE_2; RCC_PeriphClkInit.PLL2.PLL2VCOSEL = RCC_PLL2VCOWIDE; RCC_PeriphClkInit.PLL2.PLL2FRACN = 0; RCC_PeriphClkInit.FmcClockSelection = RCC_FMCCLKSOURCE_PLL2;

配置的是PLL2的时钟参数,这看上去貌似也没什么问题。但为什么会PLL2的时钟初始化失败呢?

首先找原因: 1、是不是晶振坏了? 2、是不是系统时钟哪里写错了? 3、是不是FMC时钟初始化在代码中的位置不对?经过一系列排查,发现都是没问题的,并没有解决的实际问题。任然是初始化SDRAM的时候卡在while(1)中,也就是FMC时钟参数配置失败。

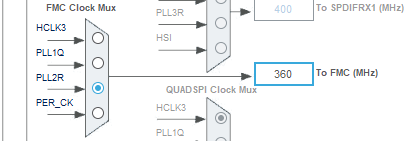

从新回到STM32H7的时钟树上!有一个我们不太看得到的点!

没错就是这里,本来在程序上应该配置的是PLL2R这个地方的时钟,用这个地方的时钟输出到FMC上,但是却是默认选择HCLK3,所以,这就是导致为什么PLL2初始化一直失败的原因!这时候将它选中PLL2Q,

没错就是这里,本来在程序上应该配置的是PLL2R这个地方的时钟,用这个地方的时钟输出到FMC上,但是却是默认选择HCLK3,所以,这就是导致为什么PLL2初始化一直失败的原因!这时候将它选中PLL2Q,  将会和预期的一样,得到360MHz的时钟。通过STM32CubeMX生成工程,后添加相关驱动文件,发现SDRAM的初始化不会再卡住了。这时候,我们比对两个工程的SystemClock_Config(),就很容易发现多了一句话,

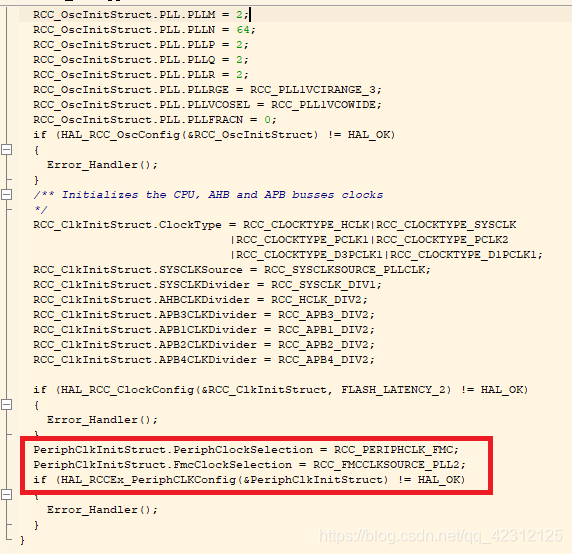

将会和预期的一样,得到360MHz的时钟。通过STM32CubeMX生成工程,后添加相关驱动文件,发现SDRAM的初始化不会再卡住了。这时候,我们比对两个工程的SystemClock_Config(),就很容易发现多了一句话,  没错,就是因为这里的选择问题,FMC的时钟源,必须选择RCC_FMCCLKSOURCE_PLL2的时候,才能对PLL2的配置生效,否则配置将ERROR。这问题搞了我一晚上,真不应该啊!

没错,就是因为这里的选择问题,FMC的时钟源,必须选择RCC_FMCCLKSOURCE_PLL2的时候,才能对PLL2的配置生效,否则配置将ERROR。这问题搞了我一晚上,真不应该啊! 发表评论

最新留言

第一次来,支持一个

[***.219.124.196]2025年04月08日 08时06分52秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

ReactJs入门教程-精华版

2021-05-09

Python 之网络式编程

2021-05-09

MySql5.5安装步骤及MySql_Front视图配置

2021-05-09

Java内存模型(JMM)

2021-05-09

AQS相关

2021-05-09

WCF学习之旅—第三个示例之一(二十七)

2021-05-09

java ThreadPoolExecutor初探

2021-05-09

快速指数算法

2021-05-09

python去除字符串中的特殊字符(爬虫存储数据时会遇到不能作为文件名的字符串)

2021-05-09

SpringCloud微服务(03):Hystrix组件,实现服务熔断

2021-05-09

Spring 框架基础(01):核心组件总结,基础环境搭建

2021-05-09

JavaEE基础(02):Servlet核心API用法详解

2021-05-09

SpringBoot2 整合Nacos组件,环境搭建和入门案例详解

2021-05-09

Sentry快速开始并集成钉钉群机器人

2021-05-09

Cassandra数据建模

2021-05-09

Internet Explorer 10 专题上线

2021-05-09

云计算之路-阿里云上:0:25~0:40网络存储故障造成网站不能正常访问

2021-05-09

网站故障公告1:使用阿里云RDS之后一个让人欲哭无泪的下午

2021-05-09