EDA设计——在 ISE 软件中 使用 VHDL 语言实现 FIFO 存储器

发布日期:2021-05-07 12:15:41

浏览次数:11

分类:原创文章

本文共 2980 字,大约阅读时间需要 9 分钟。

1. 实验内容

FIFO实验与仿真验证。

2. 实验步骤

(1) 新建工程

(2) 新建VHDL Module文件;

(3) 编写VHDL文件,编译运行;

(4) 新建仿真文件VHDL Test Bench;

(5) 编写仿真文件;

(6) 编译运行,观看仿真图形;

(7) 得出实验结果,验证是否正确。

3. 实验结果

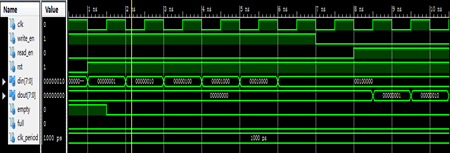

(1) 仿真激励

rst <= '0'; write_en <= '1'; wait for clk_period;rst <= '1'; din <= "00000001"; wait for clk_period;din <= "00000010"; wait for clk_period;din <= "00000100"; wait for clk_period;din <= "00001000"; wait for clk_period;din <= "00010000"; wait for clk_period;din <= "00100000"; wait for clk_period;write_en <= '0'; wait for clk_period; read_en <= '1'; wait for clk_period*10; read_en <= '0'; (2) 运行结果

4.代码附录

1.VHDL文件fifo.vhd

```clibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity fifo is port( clk : in std_logic; write_en : in std_logic; read_en : in std_logic; rst : in std_logic; din : in std_logic_vector(7 downto 0); dout : out std_logic_vector(7 downto 0); empty : out std_logic; full : out std_logic ); end fifo;architecture Behavioral of fifo is type fifo_array is array(0 to 63)of std_logic_vector(7 downto 0); signal fifo_memory : fifo_array; signal full_flag : std_logic; signal empty_flag : std_logic; signal read_add : std_logic_vector(5 downto 0); signal write_add : std_logic_vector(5 downto 0); signal counter : std_logic_vector(5 downto 0); beginprocess(rst,clk) begin if(rst='0') then dout<="00000000"; elsif(clk'event and clk='1') then if(read_en ='1'and empty_flag='0')then dout<=fifo_memory(conv_integer(read_add)); end if; end if;end process;process(clk) begin if(clk'event and clk='1')then if(rst='1'and write_en='1'and full_flag='0')then fifo_memory(conv_integer(write_add))<= din; end if; end if;end process;process(rst,clk) begin if(rst='0')then write_add<="000000"; elsif(clk'event and clk='1')then if(write_en ='1'and full_flag='0') then write_add <= write_add + 1; end if; end if;end process;process(rst,clk) begin if(rst='0') then read_add<="000000"; elsif(clk'event and clk='1') then if(read_en ='1'and empty_flag='0') then read_add <= read_add + 1; end if; end if;end process;process(rst,clk) variable temp : std_logic_vector( 1 downto 0 );begin if(rst='0')then counter<="000000"; elsif(clk'event and clk='1') then temp := read_en & write_en; case temp is when "00" => counter <= counter; when "01" => if( counter /= "111111" ) then counter <= counter + 1; end if; when "10" => if( counter /= "000000" ) then counter <= counter - 1; end if; when "11" => counter <= counter; when others => counter <= counter; end case; end if;end process;process( counter )begin if( counter = "000000" ) then empty_flag <= '1'; else empty_flag <= '0'; end if;end process;process( counter )begin if( counter = "111111" ) then full_flag <= '1'; else full_flag <= '0'; end if;end process;full <= full_flag;empty <= empty_flag;end Behavioral;发表评论

最新留言

网站不错 人气很旺了 加油

[***.192.178.218]2025年04月12日 22时42分27秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

操作系统前传第六课--开发中的辅助工具

2019-03-04

Linux系统编程44 信号 - 信号的响应过程分析!!!

2019-03-04

QT17 - 对话框及其类型 QDialog

2019-03-04

Linux系统编程67 网络编程1 - 报式套接字传输

2019-03-04

设备驱动之阻塞

2019-03-04

电平触发设备休眠唤醒--输入子系统+内核线程

2019-03-04

python数据类型

2019-03-04

机器学习之九:提升树和GBDT

2019-03-04

Ubuntu安装TensorFlow C++

2019-03-04

win10正版系统安装 win10系统启动盘制作 小白装机第一步(U盘装机)

2019-03-04

c/c++ 实参、形参、值传递、地址传递的区别与关系 ---- 授人以鱼不如授人以渔

2019-03-04

VL53L0x TOF激光测距的 stm32 HAL库驱动代码

2019-03-04

Mysql模糊查询like效率,以及更高效的写法

2019-03-04

yarn安装

2019-03-04

今天你吃汤圆了吗?

2019-03-04

CI/CD and beyond with GitHub Actions

2019-03-04

回顾 | 如何快速开发一款扩展

2019-03-04

《进击吧!Blazor!》第一章 4.数据交互

2019-03-04