《硬件架构的艺术》学习笔记(1)---亚稳态的世界

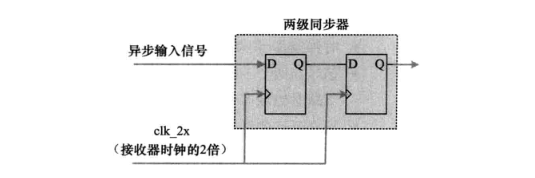

方法二:采用时钟倍频电路的多级同步器。(例如Alter的FPGA中具有这项技术)

方法二:采用时钟倍频电路的多级同步器。(例如Alter的FPGA中具有这项技术)

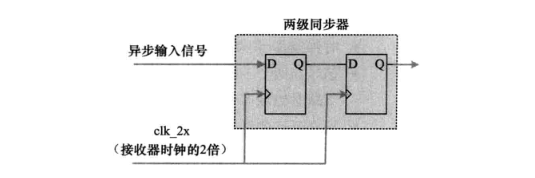

当异步输入信号的宽度小于时钟周期时,上述同步器不再适用。则采用图5的B类型同步器。

当异步输入信号的宽度小于时钟周期时,上述同步器不再适用。则采用图5的B类型同步器。  (同时保证异步输入信号的相邻脉冲之间的宽度至少大于2个采样周期,否则会来不及采样,出现采样丢失的现象)

(同时保证异步输入信号的相邻脉冲之间的宽度至少大于2个采样周期,否则会来不及采样,出现采样丢失的现象)

发布日期:2021-05-06 19:13:39

浏览次数:14

分类:精选文章

本文共 712 字,大约阅读时间需要 2 分钟。

亚稳态理论

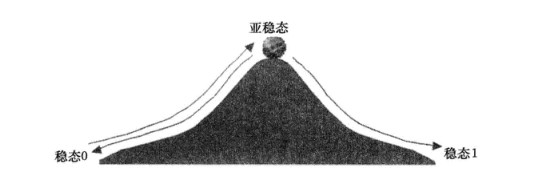

亚稳态是由于违背了触发器的建立和保持时间而产生的。如果信号在时钟上升沿前后的这段时间窗口内发生变化,那么输出将来是未知的或者称为“亚稳态”。这种有害状态的传播就叫做亚稳态。

避免亚稳态

亚稳态发生条件

以下条件中,信号可能违背时序要求:

- 输入信号是异步信号。

- 时钟偏移/摆动(上升/下降时间)高于容限值。

- 信号在两个不同频率或者频率相同相位和偏移不同的时钟域下跨时钟域工作。

- 组合延迟使触发器的数据输入在亚稳态窗口(触发器的建立和保持时间之和)内发生变化。

亚稳态避免的方法

只能减少亚稳态发生的概率,并不能从根本上完全消除亚稳态。

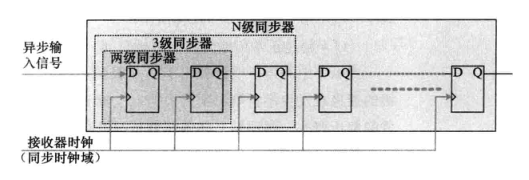

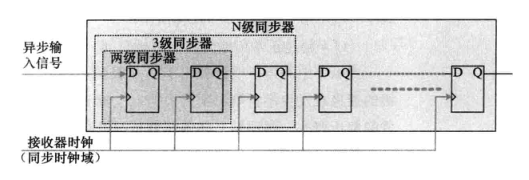

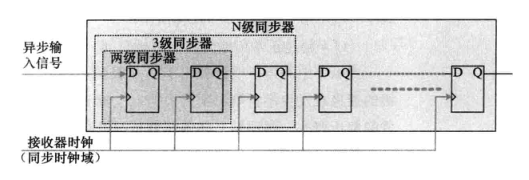

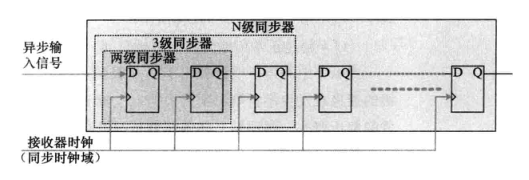

方法一:采用多级同步器的方法。用一个完整的时钟周期来解决第一级同步触发器的亚稳态问题*(不包括第二级触发器的建立时间)*。 方法二:采用时钟倍频电路的多级同步器。(例如Alter的FPGA中具有这项技术)

方法二:采用时钟倍频电路的多级同步器。(例如Alter的FPGA中具有这项技术)

同步器的类型

图4所示为类型A。对于异步输入信号比时钟周期大得多时最有效,一般采用两级同步器的结构。

当异步输入信号的宽度小于时钟周期时,上述同步器不再适用。则采用图5的B类型同步器。

当异步输入信号的宽度小于时钟周期时,上述同步器不再适用。则采用图5的B类型同步器。  (同时保证异步输入信号的相邻脉冲之间的宽度至少大于2个采样周期,否则会来不及采样,出现采样丢失的现象)

(同时保证异步输入信号的相邻脉冲之间的宽度至少大于2个采样周期,否则会来不及采样,出现采样丢失的现象)

发表评论

最新留言

表示我来过!

[***.240.166.169]2025年04月01日 12时58分54秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

VMware vSphere 离线虚拟机安装 BIND 9

2021-05-09

说说第一份工作

2021-05-09

dojo/request模块整体架构解析

2021-05-09

dojo/aspect源码解析

2021-05-09

Web性能优化:What? Why? How?

2021-05-09

Javascript定时器学习笔记

2021-05-09

dojo的发展历史

2021-05-09

Liunx百宝箱(Centos补充)

2021-05-09

Python存储系统(Redis)

2021-05-09

C语言指针收藏

2021-05-09

.net 4种单例模式

2021-05-09

T4 生成数据库实体类

2021-05-09

C#搞个跨平台的桌面NES游戏模拟器

2021-05-09

手把手教你安装Eclipse最新版本的详细教程 (非常详细,非常实用)

2021-05-09

《带你装B,带你飞》pytest成魔之路4 - fixture 之大解剖

2021-05-09

互联网App应用程序测试流程及测试总结

2021-05-09

根据轨迹分析出用户家在哪

2021-05-09

PostgreSQL查询表名称及表结构

2021-05-09

是什么?评估分类器的常用概念----准确率,精确率,召回率

2021-05-09

linux中使用awk命令

2021-05-09