本文共 3177 字,大约阅读时间需要 10 分钟。

文章目录

1 构造实现连续加法的电路

1.1 构造实现连续加法的电路

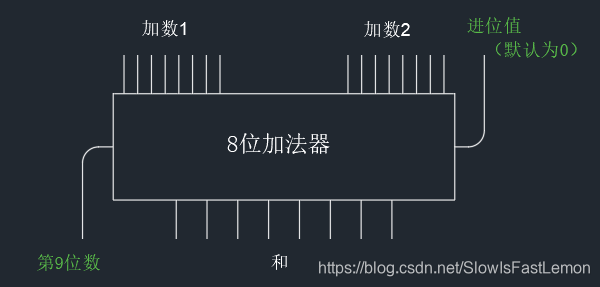

我们先来看一下我们之前构造的8位加法器:

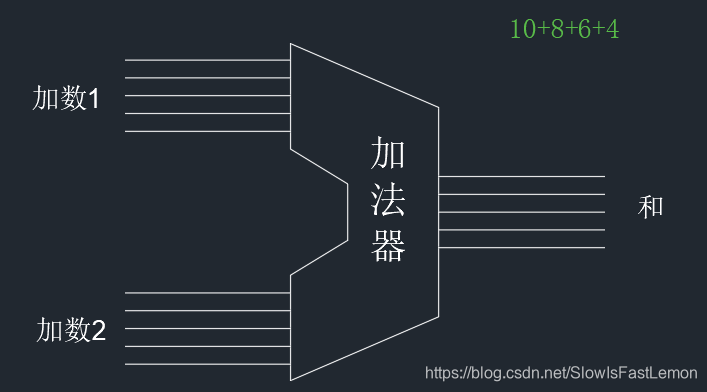

如果我们现在要计算10+8+6+4的和,对于中间结果需要我们手动保存:

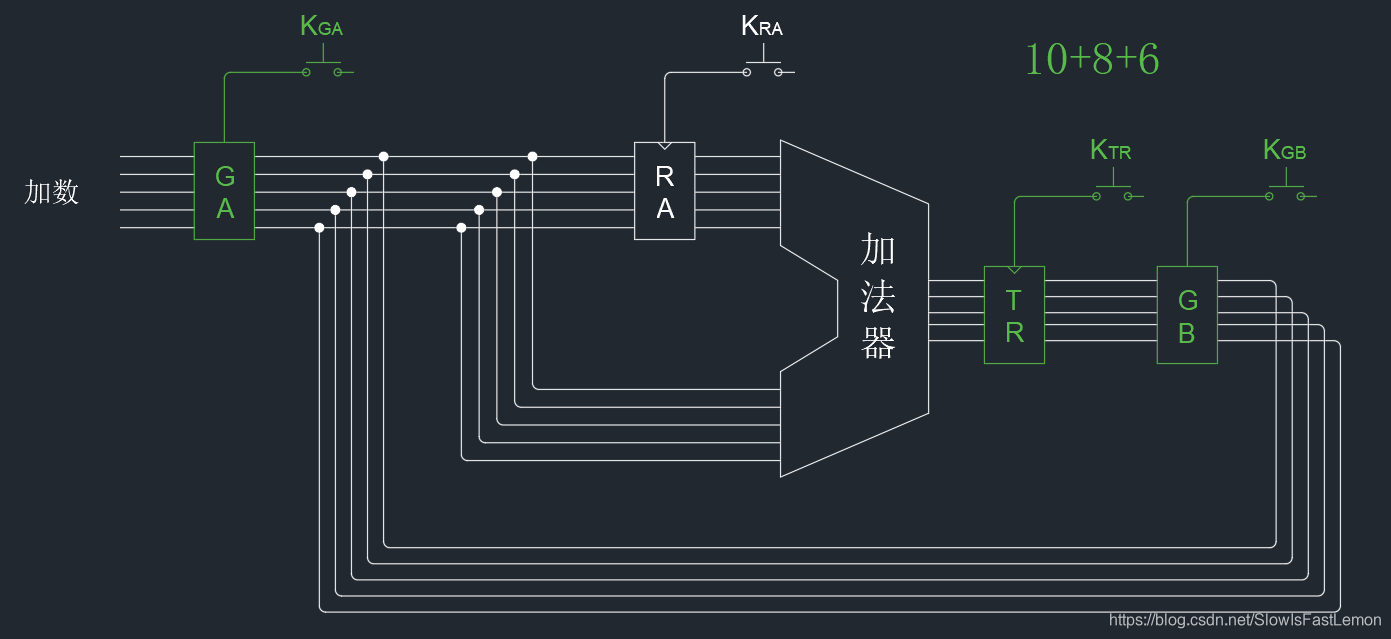

如果我们现在要计算10+8+6+4的和,对于中间结果需要我们手动保存:  能不能让加法器自己记住这个中间结果,并使其自动的参与和下一个加数的运算呢?这样的话,肯定需要将加法的结果与输入相连,我们为了从同一总线获得两个加数,我们需要做出如下改进:

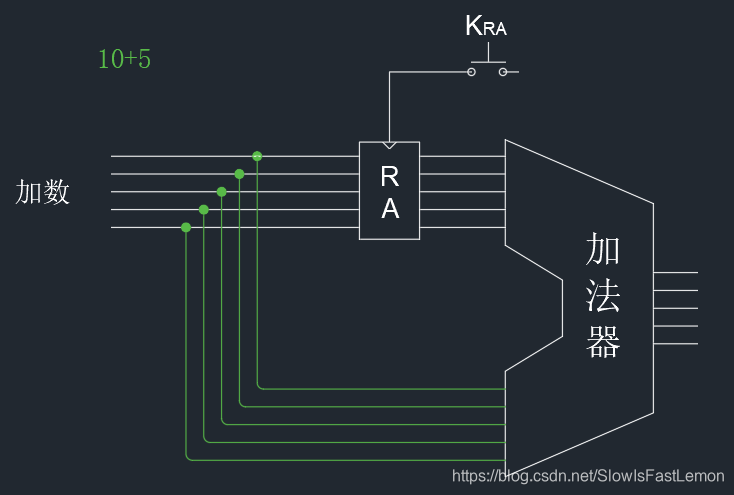

能不能让加法器自己记住这个中间结果,并使其自动的参与和下一个加数的运算呢?这样的话,肯定需要将加法的结果与输入相连,我们为了从同一总线获得两个加数,我们需要做出如下改进:  这样的话两个加数就可以依次输入,输入第一个加数时,我们按一下KRA这样第一个加数就被存储到RA寄存器中,然后输入第二个加数,即可得到加法的结果。

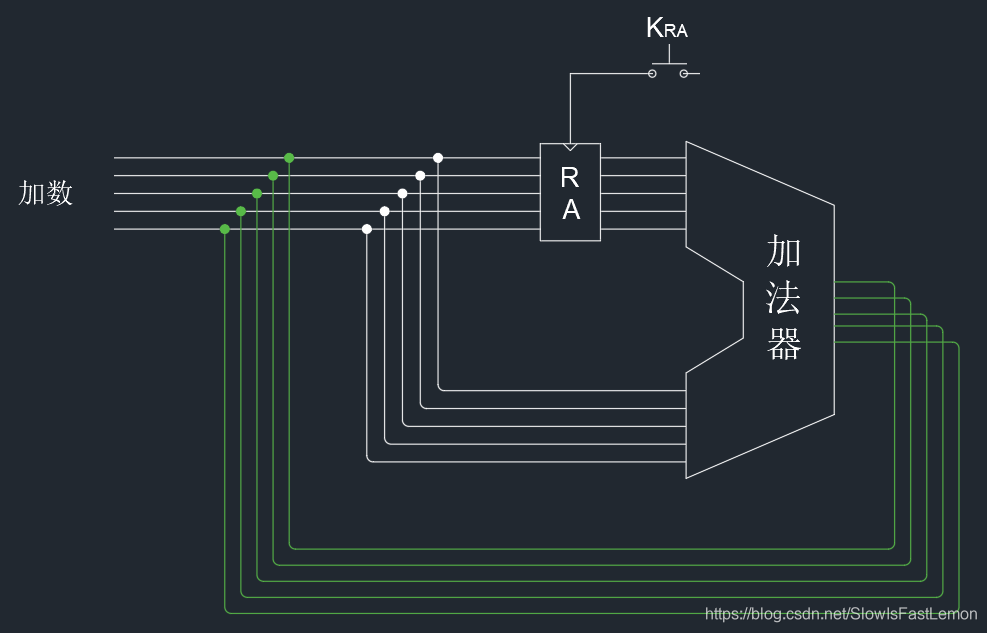

这样的话两个加数就可以依次输入,输入第一个加数时,我们按一下KRA这样第一个加数就被存储到RA寄存器中,然后输入第二个加数,即可得到加法的结果。 我们将加法器的输出反馈到加法器的加数输入:

- 加法的输出结果直接接到输入值,会造成不断进行加法,加法的值越来越大。

- 加法的输出值和加数输入值接到一起,会造成总线冲突。

我们对电路做出如下改进:

我们增加了一个寄存器TR和两个多路继电器GA、GB。我们可以通过如下方式进行计算10+8+6的值:

我们增加了一个寄存器TR和两个多路继电器GA、GB。我们可以通过如下方式进行计算10+8+6的值: - 输入加数10,按下KGA不松,按下KRA,松开KGA(这就将第1个加数进行了输入)。

- 输入加数8,按下KGA不松,这时候加法器将输出10+8=18,我们按下KTR锁存加法值,松开KGA,按下KGB不松开,按下KRA将18锁存,松开KGB。

- 输入加数6,按下KGA不松,这个时候得到18+6的值24,按下KTR,锁存结果,松开KGA。

其实我们可以将上面的操作分解为如下3个基本动作:

- 加载:其实就是输入第一个加数(KGA-KRA)。

- 相加:其实就是输入下一个加数,然后和上一个加数进行相加,并将结果存储起来(KGA-KTR)。

- 记忆:其实就是将中间结果锁存在加法器上面的输入端,以备参与下次的运算(KGB-KRA)。

1.2 对连续加法的电路进行优化

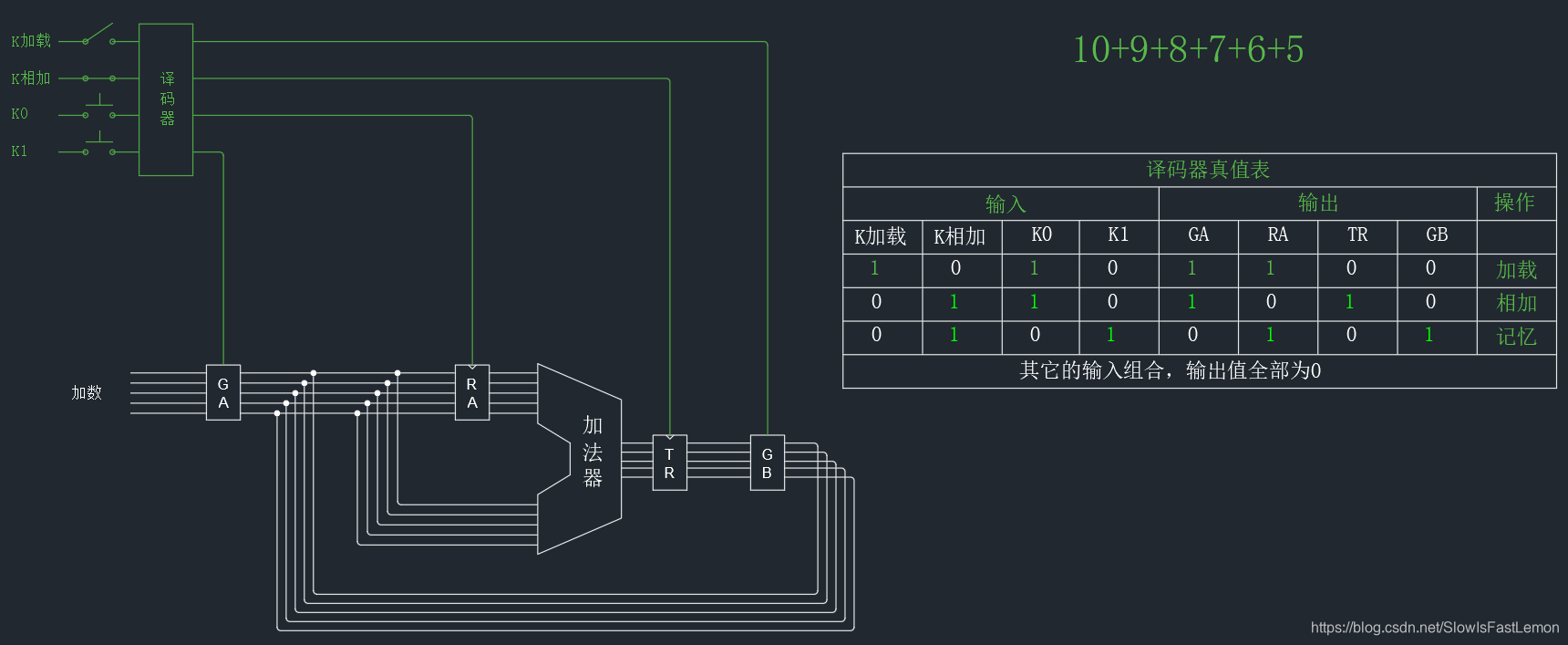

优化的电路如下:

对于上述电路分析如下: 对于加载来说,当K加载为1、K1为1时,GA和RA输出1,但是我们需要保证GA先输出1,然后RA再输出1,这部分电路的搭建放到后面再进行介绍。同样,相加、记忆中也存在同样的先后问题。

对于上述电路分析如下: 对于加载来说,当K加载为1、K1为1时,GA和RA输出1,但是我们需要保证GA先输出1,然后RA再输出1,这部分电路的搭建放到后面再进行介绍。同样,相加、记忆中也存在同样的先后问题。 对于计算10+9+8+7+6+5我们需要进行如下操作:

- 加载10。

- 相加10+9。

- 记忆19。

- 相加19+8。

- 记忆27。

- 相加27+7。

- 记忆34。

- 相加34+6。

- 记忆40。

- 相加40+5。

我们可以发现前两个数的相加并没有节省计算步骤,但是从第4步往后,我们只需要分别点击K0、K1就可完成计算。

1.3 解决先后问题

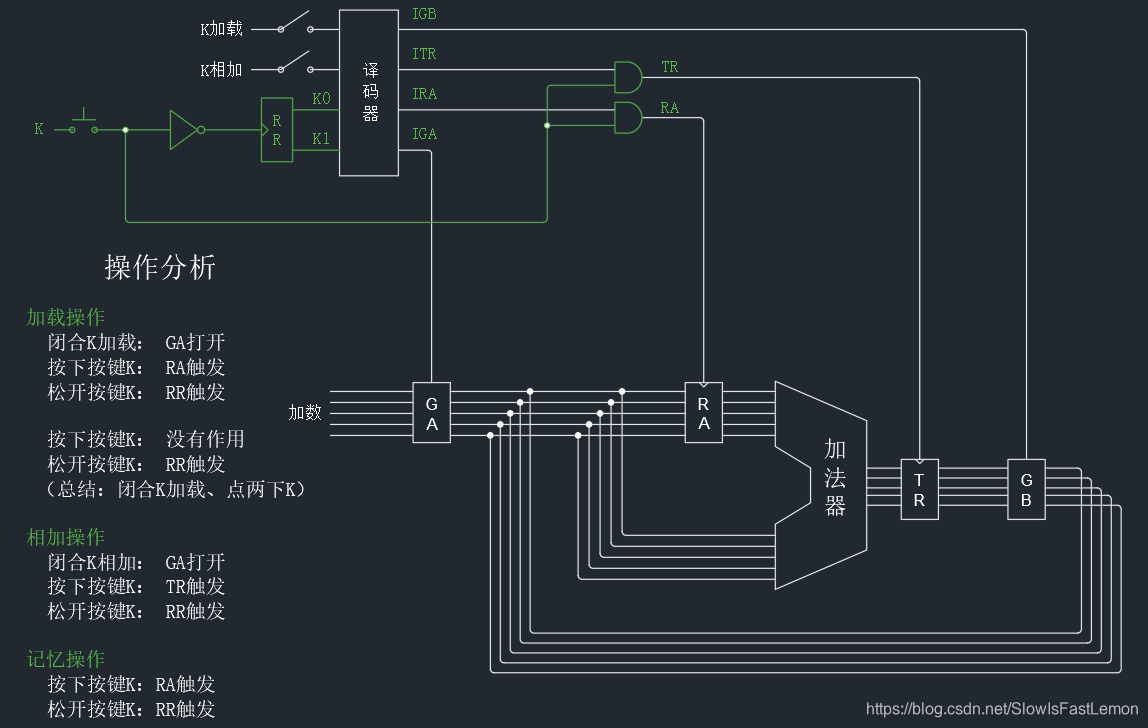

改进后的电路如下:

我们先大致看一下都有哪些改动,因为我们做加法运算的大部分操作,就是不断地点击K0和K1。而这些操作,在本质上就是1在它俩之间不断地循环。这样,我们就很容易想到,我们之前所学的循环移位寄存器。所以,我们使用了一个有两个输出的上升沿触发的循环移位寄存器RR来代替K0和K1这两个开关,来给译码器提供输入。并且,在初始状态下,K0=1,K1=0。

我们每触发一次RR,它们的值就会进行一次交替,而触发信号是由按键K来产生的,并且它们之间还加了一个非门。然后,译码器的每个和寄存器相连的输出端都要和按键K的另一路输出进行与运算。

现在,我们就来演示一下改造后的电路是如何工作的,它又是如何帮我们解决先后问题的:

首先在加数端口输入第一个加数。然后,闭合K加载,这时,由于K0=1,所以IGA=1、IRA=1,传输门GA打开,数据被传送到了RA的门口,但是RA没有被触发,因为IRA要和K的另一路输出进行与运算。我们可以发现,我们只是闭合了K加载,传输门GA就被打开了。关键点在于,我们之前需要按下K0开关才能使K0的值=1,而现在,K0的值默认就=1。所以,我们不再需要手动的去设置它的值,只要闭合K加载就可以了。

那为什么RA没有被触发呢?因为,虽然IRA=1,但是它需要和K的另一路输出做与运算。而我们并没有按下按键K,只是闭合了K加载而已,所以它不会被触发。

接下来,我们按下按键K,随着K的接通,将同时产生两路脉冲。第一路通过非门到达循环移位寄存器,但是非门将上升沿变成了下降沿,所以,循环移位寄存器并没有被触发。所以,译码器将保持原来的输出,不会发生变化。与此同时,另一路脉冲被送到了与IRA相连的与门,结果就是RA从0变成了1,产生了一个上升沿,寄存器RA被触发第一个加数就被加载到了加法器中。

然后,当我们松开K按键时,会产生一个下降沿,而这个下降沿通过非门后变成了一个上升沿,RR被触发,这时K0变成了0、K1变成了1,这时,译码器所有的输出都=0。

我们通过闭合K加载,来打开传输门,通过按下K按键,来触发寄存器。这样,我们就解决了先后的问题。同时大家要注意RR循环移位寄存器被触发的时间,它是在K按键被松开的时候触发的。

尽管现在我们已经完成了加载操作,但是我们需要再按一次按键K。按下的时候,第一路输出不会触发RR寄存器。第二路输出,因为译码器的输出全部是0,所以也不会触发任何一个寄存器。也就是说,在按下的时候,并不会产生任何作用。而松开的时候,会触发RR,使得K0=1、K1=0,这也是我们的目的所在:使RR回到初始状态。因为,我们的下一步是相加,而相加操作时,K0的值为1。

总结来说加载操作是这样的,闭合K加载,然后点两下K。这样不但完成了加载操作,同时还为下一步的相加操作做好了准备。

接着,我们开始执行相加操作。首先在加数端口输入第二个加数。然后,断开K加载,闭合K相加,这时,由于K0=1,所以,IGA=1、ITR=1,传输门GA打开,数据进入加法器并和第一个数进行相加,并且结果被送到了TR门口。但是TR没有被触发,因为ITR还需要和按键K的另一路输出进行与运算。现在,按下按键K,因为非门的存在,所以RR没有被触发。但是,按键K的另一路脉冲和ITR做与运算,结果就是TR从0变成了1,产生一个上升沿,TR被触发,相加的结果被存储在TR寄存器中。

接着,松开按键K,RR被触发,于是,K0=0、K1=1。这就为记忆的操作提前做好了准备。

现在,我们开始执行记忆操作。因为K相加已经是闭合状态,所以我们不需要再去改动它,而且K1已经=1了。所以这时,传输门GB打开,中间结果被传送到了RA的门口。然后我们按下按键K,因为非门的存在,所以RR依然没有被触发。但是,RA被触发,因为按键K的第二路输出和IRA做与运算被触发后,RA将中间结果存储在了加法器中。然后松开按键K,RR被触发,使得K0=1、K1=0,RR又重新回到了最初始的状态,为下一次相加操作做好了准备。

现在,我们的操作就变成了这样。闭合K加载、点2下K,完成第一个加数的加载。断开K加载、闭合K相加、点两下K,完成第二个加数相加和记忆。

这时,K相加是闭合的,所以,我们不再需要去操作它。直接点两下K,就完成了第三个数的相加和记忆。再点两下K,就完成了第四个数的相加和记忆。每点两下K就完成了对一个数的运算,直到加完最后一个数为止,而最终的结果存储在RA寄存器中 。

我们来总结一下这个电路运行的特点:

第一个特点: 闭合K加载或者K相加,就会直接打开某一个传输门。因为,K0和K1的值不需要我们手动的去设置。而且,与传输门相连的输出端和传输门之间是直接连通的。第二个特点:

必须按下K按键,寄存器才会被触发。因为,与寄存器相连的输出端要和K的输出进行与运算。所以,不按下K,寄存器是不会被触发的。现在,我们不但解决了先后的问题,而且进一步简化了操作。因为,K0、K1这两个开关被K这一个开关取代了,之前,我们需要对K0和K1这两个开关进行操作,而现在,我们的大部分操作基本上就变成了不断地输入加数,然后点击按键K就可以了。

参考资料:

转载地址:https://muzimin.blog.csdn.net/article/details/103682422 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关于作者