本文共 2316 字,大约阅读时间需要 7 分钟。

本文是一个衔接点,上一篇文章以前都是学习8086实模式的知识。本文开始学习80386这种现代处理器的编程架构。由此进入保护模式的学习。点击链接查看上一篇文章:

1、现代处理器的结构和特点

1 流水线技术

处理器可以做很多事情,能够执行各种不同的指令,完成不同的功能,但这些事情大多不会再一个时钟周期内完成。执行一条指令,需要从内存中取指令,译码,访问操作数和结果,并进行移位、加法、减法、乘法以及其他任何操作。

为了提高处理器的执行效率和速度,可以把一条指令的执行过程分解成若干个细小的步骤,并分配给相应的单元来完成。各个单元的执行都是独立的、并行的。如此一来,各个步骤在时间上就会重叠起来,这种执行指令的方法,就是流水线(Pipe-Line)技术。

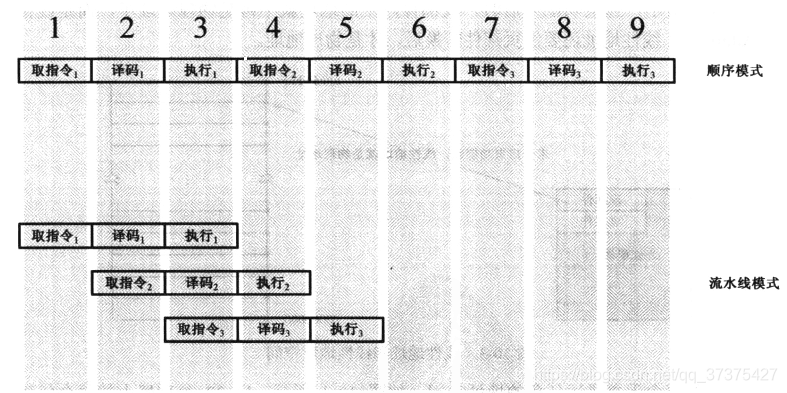

比如,一条指令的执行过程分为取指令、译码和执行三个步骤的话。假设每个步骤都要花一个时钟周期,那么如下图所示,如果采用顺序执行,则执行三条指令就要花9个时钟周期,没3个时钟周期才能得到一条指令的执行结果;如果采用3级流水线技术的话,则执行这三条指令只需要5个时钟周期,每隔一个时钟周期就能够得到一条指令的执行结果。

2、高速缓存技术

高速缓存,在以前的文章中有讲的很详细,这里不再赘述,直接查看以前的文章即可。

点解下面链接查看:

其实简单来说高速缓存就是为了弥补外存(内存条)的读写速度过于缓慢的缺陷。将内存中的一些指令和数据,缓存到高速缓存中,那么CPU可以不用访问内存而直接访问高速缓存,这样会快的多!!!

3、乱序执行技术

为了实现流水线技术,需要将指令拆分成更小的可独立执行部分,即拆分成微操作。

一旦将指令拆分成微操作,处理器就可以在必要的时候乱序执行。考虑以下程序:

mov eax , [mem1]shl eax , 5add eax , [mem2]mov [mem3] , eax

这里add eax , [mem2]可以拆分成两个微操作。先从mem2对应的地址取数据,然后将数据与eax寄存器中存的数据相加,得到的结果存入eax寄存器。如此一来,在执行逻辑左移指令的同时,处理器可以提前从内存中读取mem2的内容。典型的,如果数据不在高速缓存中,那么处理器在获取mem1的内容后,会立即开始获取mem2的内容,与次同时,shl指令的执行早就开始了。

类似的这种乱序执行很多很多,总给不在赘述。

4、寄存器重命名技术

考虑以例子:

mov eax , [mem1]shl eax , 3mov [mem2] , eaxmov eax , [mem3]add eax , 2mov [mem4] , eax

以上代码做了两件事情,但是互不相干。

- 将mem1的内容左移3次后,传给mem2

- 将mem3的内容加2后,传给mem4

如果我们为最后三条指令使用不同的寄存器,就更能清楚的看明白,这两件事的互不相干性。事实上,处理器也是这么做的。处理器为最后三条指令使用了另一个不用的临时寄存器,因此,左移和加法指令可以并行的处理。

IA-32架构的处理器只有8个32位的通用寄存器,但通常都会被我们全部派上用场(甚至还觉得不够)。因此我们不能奢望在每个计算机中都使用新的寄存器。不过在处理器内部,却有大量的临时寄存器可用,处理器可以重命名这些寄存器,但是以代表一个逻辑寄存器,比如上述的EAX寄存器。

寄存器重命名以一种完全自动和非常简单的方式工作。每当指令写一个逻辑寄存器时,处理器就为那个逻辑寄存器分配一个新的临时寄存器。

在所有操作都完成之后,那个代表EAX的临时寄存器里面存的内容就会被写入真实的EAX寄存器,该处理过程称为引退。

所有通用寄存器,栈指针寄存器,标志寄存器,浮点寄存器,甚至段寄存器都有可能被重命名。

5、 分支目标预测技术

流水线并不是百分之百完美的解决方案。实际上,有很多潜在的因素会使得流水线不能达到最佳的效率。一个典型的情况是,如果遇到一条转移指令,则后面那些已经进入流水线的指令就都无效了。换句话说,我们必须清空流水线,从要转移到的目标位置处重新取指令放入到流水线。

随着复杂架构下的流水线变得越来越长,程序分支带来的问题变得很大。为了解决这个问题,引入了分支预测技术。

从统计学的角度来看,有些事情一旦发生,下一次发生的概率很大。比如下面的程序片段:

xor si , si lops: ...... cmp si , 20 jnz lops

当jnz指令第一次执行时,转移一定会发生。那么处理器就可以预测,下一次它还会转移到标号lops处,而不是顺序往下执行。事实上,这个预测通常是很准的。

在处理器内部,有一个小容量的高速缓存器,叫做 分支目标缓存器(BTB)。当处理器执行了一条分支语句后,它会在BTB中记录当前指令的地址、分支目标的地址。以及本次分支预测的结果。下一次,在那条转移指令实际执行之前,处理器会查找BTB中,看有没有最近的转移记录。如果能找到最近的条目,则推测执行和上次相同的分支,把该分支的指令送入流水线。

当该指令执行时,如果预测是失败的,那么清空流水线,同时刷新BTB中的记录。这个代价很大。

细心的人早已发现,这其实就是一个缓存的思想!!!这个思想很牛逼!!!

2、总结

理解现代处理器的结构特点:

- 流水线技术

- 高速缓存思想

- 乱序执行思想

- 寄存器重命名

- 分支目标预测技术

其实这些思想,在以后的上层软件开发中,也是经常遇到。

笔记记得不是很全,如果有不懂的可以加我联系方式一起交流。

学习探讨加个人:

qq:1126137994 微信:liu1126137994转载地址:https://lyy-0217.blog.csdn.net/article/details/84951309 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关于作者