Makefile 文件中的:obj-$(CONFIG_TEST) += test.o,这一类的是什么意思?

发布日期:2021-06-30 18:55:32

浏览次数:2

分类:技术文章

本文共 516 字,大约阅读时间需要 1 分钟。

1、obj-$

$(CONFIG_TEST) 是一个整体,$(bbb)表示引用变量 bbb

比如定义 CONFIG_TEST=y

$(CONFIG_TEST) 就是 y

obj-$(CONFIG_TEST) 就是 obj-y

又比如定义 CONFIG_TEST=m

$(CONFIG_TEST) 就是 m

obj-$(CONFIG_TEST) 就是 obj-m

obj-y += foo.o 该例子告诉Kbuild在这目录里,有一个名为foo.o的目标文件。foo.o将从foo.c 或foo.S文件编译得到。

例子:

obj-$(CONFIG_FOO) += foo.o $(CONFIG_FOO)可以为y(编译进内核) 或m(编译成模块)。如果CONFIG_FOO不是y 和m,那么该文件就不会被编译联接了 除了y、m以外的obj-x 形式的目标都不会被编译。 除了obj-形式的目标以外,还有lib-y library 库、hostprogs-y 主机程序等。

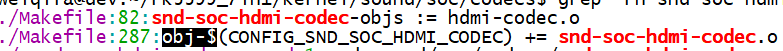

2、objs用法

obj-y = main.o main-objs := a.o \ b.o \ c.o 将a.c b.c c.c三个文件编译后链接生成main.o

转载地址:https://linus.blog.csdn.net/article/details/87854888 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

初次前来,多多关照!

[***.217.46.12]2024年04月30日 14时32分10秒

关于作者

喝酒易醉,品茶养心,人生如梦,品茶悟道,何以解忧?唯有杜康!

-- 愿君每日到此一游!

推荐文章

POJ-2418 Hardwood Species(Trie树)(map)

2019-04-30

HDU-4300 Clairewd’s message + 4333(扩展KMP)

2019-04-30

HDU 1592 Half of and a Half(高精度)

2019-04-30

POJ-3304 Segments(计算几何)

2019-04-30

UVA-11538 Chess Queen(数学)

2019-04-30

UVA-11401 Triangle Counting(数学优化)

2019-04-30

Codeforces Round #369 (Div. 2)

2019-04-30

UVA 11426 GCD - Extreme (II)(欧拉函数)

2019-04-30

HDU-2838 Cow Sorting(树状数组)

2019-04-30

POJ-2299 Ultra-QuickSort(树状数组)(离散化)

2019-04-30

基于SSM的兼职论坛系统的设计与实现

2019-04-30

基于java的图书管理系统的设计与实现

2019-04-30

基于java的SSM框架理财管理系统的设计与实现

2019-04-30

基于java的ssm框架就业信息管理系统的设计

2019-04-30

基于java的ssm框架的旅游网站设计与实现

2019-04-30

基于java的SSM框架的流浪猫救助网站的设计与实现

2019-04-30

基于java的SSM框架的教务关系系统的设计与实现

2019-04-30

别再问我什么是A/B测试了!

2019-04-30

如何用同期群分析模型提升留存?(Tableau实战)

2019-04-30