本文共 1057 字,大约阅读时间需要 3 分钟。

解决CPU,内存,I/O设备之间的速度差

- CPU 增加了缓存,以均衡与内存的速度差异。// 导致

可见性问题 - 操作系统增加了进程、线程,以分时复用 CPU,进而均衡 CPU 与 I/O 设备的速度差异。// 导致

原子性问题 - 编译程序优化指令执行次序,使得缓存能够得到更加合理地利用。// 导致

有序性问题

可见性问题(CPU缓存造成的)

为什么要加CPU缓存

CPU缓存的容量比内存小的多但是交换速度却比内存要快得多。缓存的出现主要是为了解决CPU运算速度与内存读写速度不匹配的矛盾,因为CPU运算速度要比内存读写速度快很多,这样会使CPU花费很长时间等待数据到来或把数据写入内存。

也就是说CPU不充内存里直接读数据,而是冲CPU缓存里读数据。多核时代

首先,单核是不存在可见性问题的,为了提高计算机的性能,CPU从单核发展为多核。

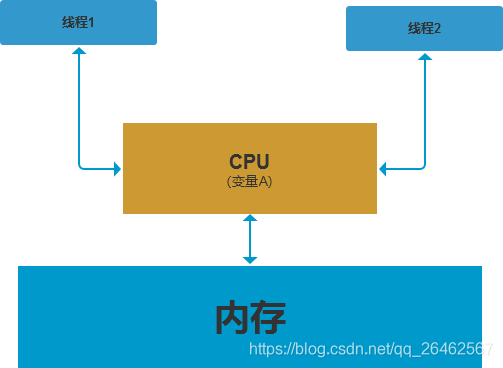

单核缓存与线程关系

对于

变量A被缓存到CPU的缓存中,线程1和线程2由同一个CPU执行,变量A对于线程1和线程2都是可见的,因此单核CPU不存在可见性问题

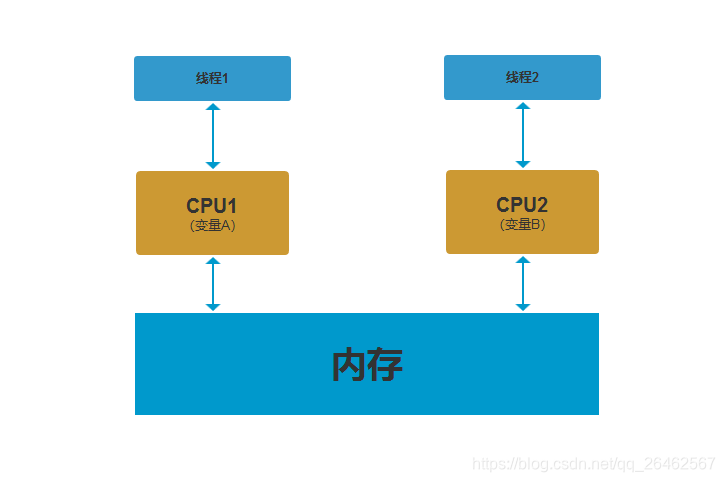

多核处理器的可见性问题

线程1由CPU1执行需要读取变量A,线程2由CPU2执行需要读取变量B,但是如果线程2要读取变量A,但是变量A在CPU1的缓存里,变量A对于线程2不可见,同理变量B对于线程1不可见

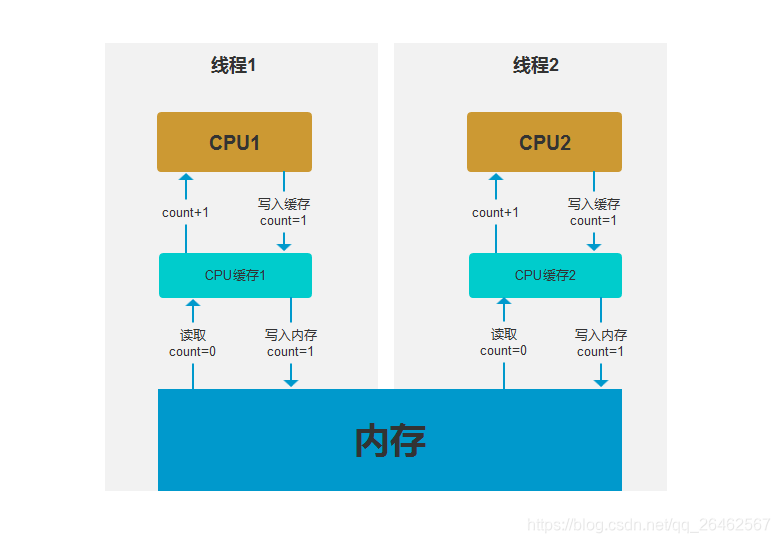

原子性问题(多线程)

线程1和线程2分别在CPU1和CPU2中执行,两个线程同时将变量count从内存中读取到CPU缓存中,线程1首先将数据处理(计数器加1)完成,然后写入内存,然后线程2将数据处理完,然后写入内存。实际上,两个线程分别对计数器进行加1,count本应该等于2。但是在这种极限的情况先count等于1,这就是原子性问题。

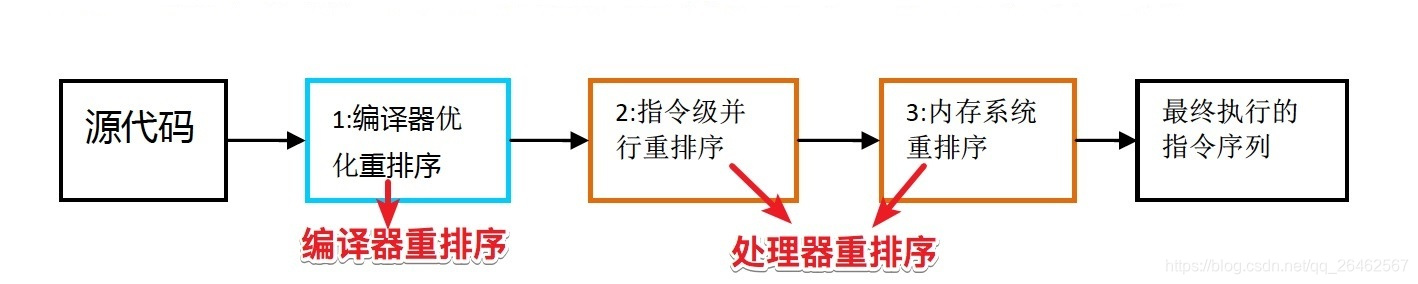

有序性问题(指令重排造成)

在说有序性之前,我们必须先来说一下指令重排,因为如果没有指令重拍的话,也就不存在有序性问题了。

指令重排是指编译器和处理器在不影响代码单线程执行结果的前提下,对源代码的指令进行重新排序执行。这种重排序执行是一种优化手段,目的是为了处理器内部的运算单元能尽量被充分利用,提升程序的整体运行效率。

重排序分为以下几种:

- 编译器优化的重排序。编译器在不改变单线程程序语义的前提下,可以重新安排语句的执行顺序。

- 指令级并行的重排序。现代处理器采用了指令级并行技术来将多条指令重叠执行。如果不存在数据依赖性,处理器可以改变语句对应机器指令的执行顺序。

- 内存系统的重排序。由于处理器使用缓存和读/写缓冲区,这使得加载和存储操作看上去可能是在乱序执行。

转载地址:https://keepgoon.blog.csdn.net/article/details/115836763 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关于作者