本文共 2329 字,大约阅读时间需要 7 分钟。

好吧,标题不对仗了......本文是笔记(七):经典组合逻辑器件(上)的后续,主要讲两类与计算相关的逻辑电路:加法器与比较器。

一、加法器

1. 半加器

最最基础的加法器,能做一位比特的加法,也就是

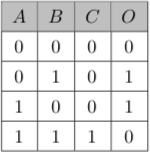

因此列出真值表:

其实在笔记(三):基本逻辑中,已经提到过,异或逻辑是二进制下的加法运算——此处我们也可以发现,

这幅图中展示了四种输入情况时不同的输出。

2. 多位加法器

一位加法器并不能使我们满足。如果我们要做的加法不止一位,比如,计算1101+0111时,如果是手算,那就会列竖式:

发现其实中间几位在做加法时,需要加三个数字,而不只是两个。考虑一个四比特的加法:

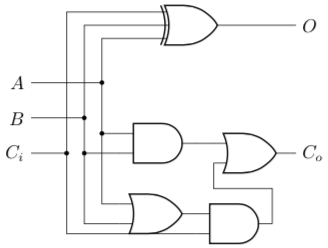

除了最低一位,其他每一位都需要处理三项输入:两个数位和一个来自低位的进位。前一节中的加法器只能有两个输入,只能处理最低一位,对于其他位,我们需要增加一个输入,也就是来自更低位的进位信号。这样,才能实现加法的扩展。完成的运算是:

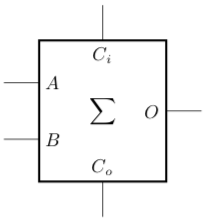

按我的习惯,会像这样表示这个加法器:

这便是一位加法器的抽象。如何将其扩展为更多位的加法器?回到加法的竖式:

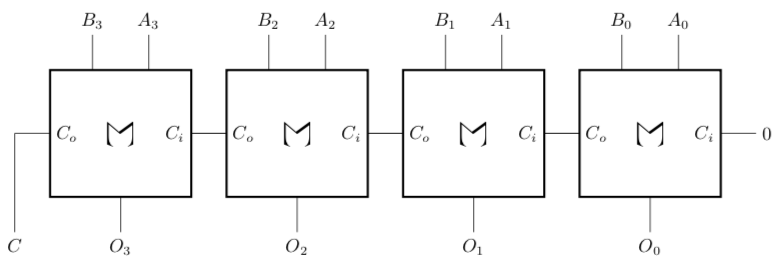

对于每一位输出,将更低位的进位和这一位对应的两个输入相加,然后把进位传递给更高位即可。这是加法器的简单“串联”。注意到,由于在上图的表示中,进位在侧面,连线时就不会和其他的输入数位混淆。

举个例子,输入

此时设计出的电路就是74HC283(虽然它采用的是超前进位而不是串行进位,但这种技术细节不是非常重要)。它能做四比特的加法——许多计算类的电路都以四比特为单位,因为四比特刚好是一个十进制或十六数字的长度。

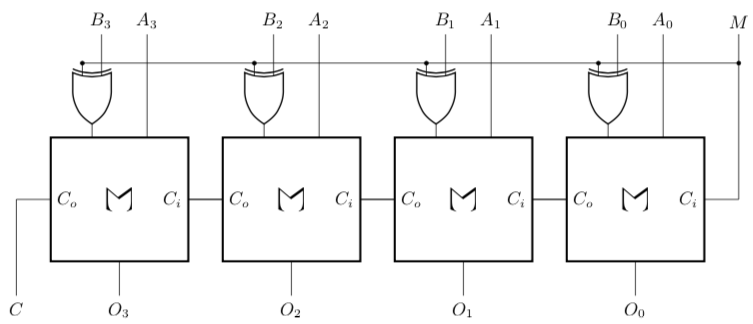

3. 减法器

计算减法,不必再使用新的元件。回顾在笔记(二):数制与编码中所提到的”补码“:

所以,如果需要做减法运算,实际上需要做两步:1. 将减数取反;2. 整体+1。其中+1一步甚至不需再做一次加法——注意到在加法器中,最低位仍然有一个低位进位

二、比较器

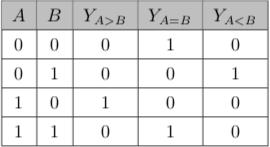

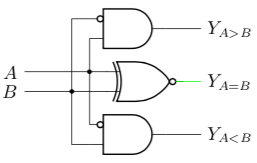

为了做运算,除了做加减法,还要能做比较——比较器能比较两个数的数值大小。两个数

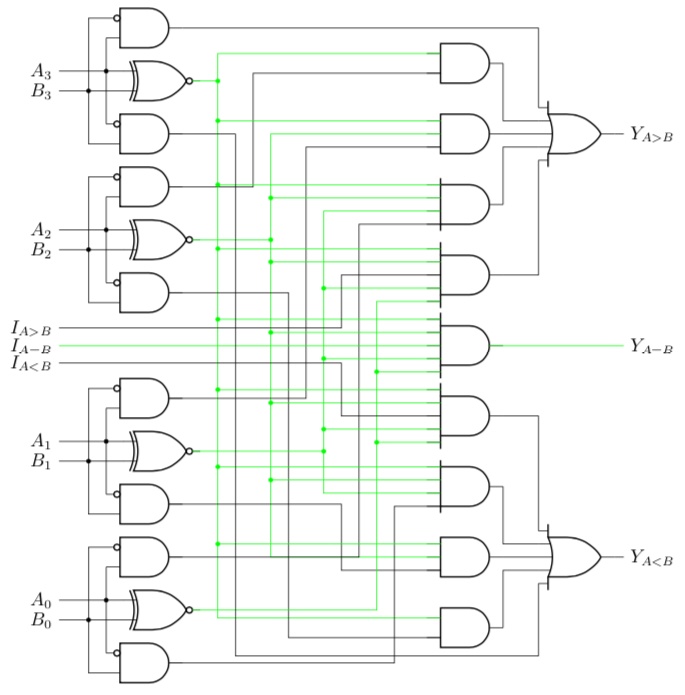

拓展到更多位数,我们会发现有优先级的存在:如果高位之间已经能比出大小,就没有必要比较更低的位数了——只有在高位相同的情况下,才需要接着比下一位。以比较

(此公式虽然看着恐怖如斯,但仔细分析,原理非常简单)

同时,和加法器的设计准则一致,为了保证可扩展性,还要再加入一个考虑,就是更低位之间的关系。为此,再加入三个端口:

这就是四位比较器74HC85的内部逻辑。

三、算术逻辑单元 (ALU)

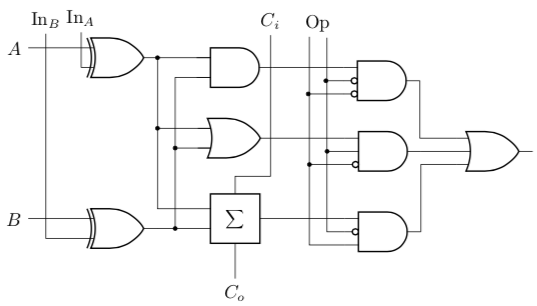

算术逻辑单元 (Arithmetic Logic Unit) 是计算机中实现数值和逻辑的基础元件——它不是实现某一特定功能的元件,而是许多功能的集合。在前文中实现了所有需要的元件之后,我们可以尝试做出一个1比特ALU。它能执行的指令包括:

ADD X1, X2, X3 //加法SUB X1, X2, X3 //减法AND X1, X2, X3 //按位与ORR X1, X2, X3 //按位或

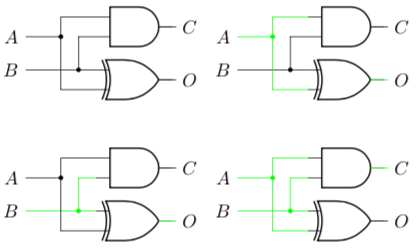

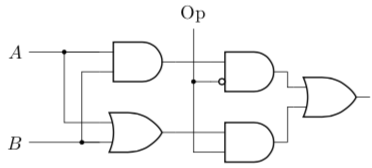

每一个指令都要接受两个参数。我们先设计按位与和按位或:每个用一个逻辑门实现,然后再用一个2选1选择器决定使用哪个输出。

这个电路当操作符Op为0时,输出

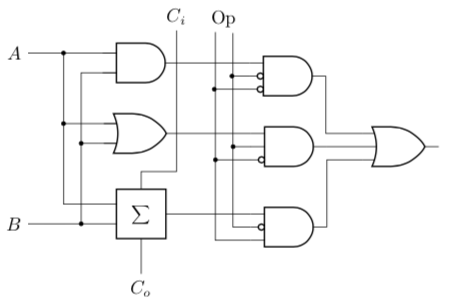

把2选1选择器扩充为了4选1,并且Op操作符也变成了两位。Op=00,做AND A, B;Op=01,做ORR A, B;Op=10,做ADD A, B。 现在ALU也拥有了进位输入输出,可以将其串联,扩展为更多位的运算。

我们继续增添减法功能。由于之前说过,减法不过是将

其中

- 0000:

A & B - 0001:

A | B - 0010:

A + B - 0110:

A - B

当然,实际的ALU的功能不止于此。在未来的某篇文章,会真正设计一个完整的ALU。

至此,我们介绍完了所有常见的组合逻辑电路,并在这其中反复展示了我们是如何一步步从需求到电路实现的,还演示了几次如何利用现有的集成电路实现更多功能。我们已经有了实现一个计算机所需要的最关键的部分之一——计算单元。从下一章开始,我们将会开始关注CPU中另一个灵魂所在——时钟和时序电路。

转载地址:https://blog.csdn.net/weixin_33565558/article/details/112141547 如侵犯您的版权,请留言回复原文章的地址,我们会给您删除此文章,给您带来不便请您谅解!

发表评论

最新留言

关于作者